# SYNCHRONIZED CLOCK MODEL 8171A

### INSTRUCTION MANUAL

# PLEASE NOTE OUR NEW ADDRESS

# **SPECTRACOM CORPORATION**

95 Methodist Hill Drive Suite 500 Rochester, New York 14623

Manual Revision 3.0 September 1987

#### WARRANTY

Spectracom Corporation warrants to the original purchaser each new instrument to be free from defects in material and workmanship for a period of one year after shipment. Repair or replacement, at our option, will be made when our examination indicates that defects are due to workmanship or materials. Electron tubes, batteries, fuses, and lamps that have given normal service are excluded from warranty coverage. All warranty returns must first be authorized in writing by the factory.

This warranty does not apply to any of our products which have been repaired or altered by persons not authorized by Spectracom Corp. or not in accordance with instructions furnished by us. If the instrument is defective as a result of misuse, improper repair, or abnormal conditions or operations, or if any serial number or seal has been removed or altered, the warranty is void and repairs will be billed at cost.

This warranty is in lieu of all other obligations or liabilities expressed or implied and Spectracom Corp. neither assumes nor authorizes any person to assume for them, any other liability in connection with sales of its products.

#### REPAIR AND MAINTENANCE

Instruments should be returned only upon prior written authorization from Spectracom Corp. or its authorized sales and service representative. Warranty repair will be made upon written request. Please provide the following information in order to enable us to serve you efficiently:

- 1. Model Number and type

- 2. Serial Number

- 3. Description of trouble

- 4. Conditions and hours of use

Upon receipt of this information our service department will send you service data or shipping instructions. Transportation to the factory is to be prepaid by the purchaser.

For assistance contact your nearest Spectracom sales representative.

#### WARRANTY REGISTRATION

Spectracom Corporation 95 Methodist Hill Dr. Ste 500 Rochester, NY 14623

Dear Customer,

Spectracom occasionally contacts customers regarding our products. We must know to whom we should send manual updates, change notices, and new product information. Because people sometimes change job assignments, we request department, mail station, and title information to ensure that correspondence in future years will reach either the user of our products or his/her supervisor. In filling out the registration, please use the title/mail station/department of the supervisor most interested in keeping the equipment and its documentation up-to-date. Thank you.

| Name                      |                                         | Title          |                                         |

|---------------------------|-----------------------------------------|----------------|-----------------------------------------|

| Department                |                                         | Mail Stop      | * · · · · · · · · · · · · · · · · · · · |

| Company                   |                                         | Model Number   |                                         |

| Address                   |                                         | Serial No.     |                                         |

| City                      | • • • • • • • • • • • • • • • • • • • • | Date Installed |                                         |

| State                     | Zip                                     |                |                                         |

| Telephone                 | Ext.                                    | -              |                                         |

| Remarks (problems, sugges | tions, et                               | c.):           |                                         |

|                           |                                         |                |                                         |

|                           |                                         |                |                                         |

|                           |                                         |                |                                         |

#### CERTIFICATE OF TRACEABILITY

SPECTRACOM CORPORATION hereby certifies that its Model 8171A Synchronized Clock provides direct traceability to the National Bureau of Standards, when operated in conjuction with a Spectracom WWVB Receiver with time code output.

When properly installed and maintained, the Model 8171A provides time accuracy and output resolution as published in the equipment's instruction manual.

SPECTRACOM CORPORATION

#### IMPORTANT INSTALLATION NOTICE

The Model 8171A operates in conjunction with a WWVB receiver (Models 8160A, 8161, or 8164). Data is transmitted via an RS-422 bus. The cable must be terminated at both ends in it's characteristic impedance.

To accomplish this, connect a terminator plug (Spectracom Part Number 015504) to the BUS A connector of the Model 8171A unit which is connected to a WWVB reciever. This termination is required even if only one Model 8171A unit is utilized.

If additional Model 8171A units are to be daisy-chained to the first 8171A unit's bus, connect a terminator receptacle (Spectracom Part Number 015505) to BUS B of the last Model 8171A in the chain.

For further details, refer to Section 1.2.9, and Figure 1-3 of this manual.

### CONTENTS

| MISCELLANEOUS |                       |                             | PAGE |

|---------------|-----------------------|-----------------------------|------|

|               | Importa               | ant Installation Notice     |      |

|               | Warranty Registration |                             |      |

|               | Warrant               |                             |      |

|               |                       | icate of Traceability       |      |

|               |                       |                             |      |

| SECTION 1     | 8171A I               | Installation & Operation    |      |

| 1.1           | Introdu               | uction                      | 1-1  |

|               |                       |                             |      |

| 1.2           | Install               | ation                       | 1-1  |

|               | 1.2.1                 | Unpacking                   | 1-1  |

|               | 1.2.2                 | Reshipment                  | 1-1  |

|               | 1.2.3                 | Input power                 | 1-2  |

|               | 1.2.4                 |                             | 1-2  |

|               | 1.2.5                 | Bench Operation             | 1-2  |

|               | 1.2.6                 | Rack Mount (Option 01)      | 1-2  |

|               | 1.2.7                 |                             | 1-2  |

|               | 1.2.8                 |                             | 1-4  |

|               | 1.2.9                 |                             | 1-5  |

|               | 1.2.10                |                             | 17   |

|               |                       |                             |      |

| 1.3           | Operati               |                             | 1-8  |

|               | 1.3.1                 | Front Panel Functions       | 1-8  |

|               | 1.3.2                 |                             | 1-8  |

|               | 1.3.3                 |                             | 1-9  |

|               | 1.3.4                 |                             | 1-10 |

|               | 1.3.5                 | <b>J</b>                    | 1-12 |

|               | 1.3.6                 | Time Flags                  | 1-13 |

|               | 1.3.7                 | Time Code Format            | 1-13 |

|               | 1.3.8                 | Propagation Path Delay      | 1-14 |

| 1.4           | Specifi               | cations                     | 1-17 |

|               | 1.4.1                 |                             | 1-17 |

|               | 1.4.2                 |                             | 1-17 |

|               |                       | AUX IN/OUT                  | 1-18 |

|               | 1.4.4                 | 1 PPS On-Time Output        | 1-19 |

|               | 1.4.5                 | 1-MHz Standby Input         | 1-19 |

|               | 1.4.6                 | IRIG Output                 | 1-19 |

|               | 1.4.7                 | 366/365 Switch              | 1-19 |

|               | 1.4.8                 | Time Zone Switch            | 1-19 |

|               | 1.4.9                 | Path Delay Switch           | 1-19 |

|               | 1.4.10                | Remote Output Connector     | 1-20 |

|               | 1.4.11                | Serial ASCII                | 1-21 |

|               | 1.4.12                | Bus B                       | 1-21 |

|               | 1.4.13                | Bus A                       |      |

|               |                       |                             | 1-22 |

|               | 1.4.14                | Parallel BCD - Option 18    | 1-22 |

|               | 1.4.15                | Time Sync                   | 1-22 |

|               | 1.4.16                | Stand-by Crystal Oscillator | 1-22 |

|               | 1.4.17                |                             | 1-23 |

|               | 1.4.10                | Options in numerical order  | 1-23 |

### CONTENTS

| SECTION 2 | Theory of Operation                                                                                                                                                                 | PAGE                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.1       | Introduction                                                                                                                                                                        | 2-1                              |

| 2.2       | Microprocessor Assembly, Part Number 015500                                                                                                                                         | 2-1                              |

| 2.3       | Display Assembly, Part Number 014100                                                                                                                                                | 2-14                             |

| 2.4       | DC Power Supply Assembly, Part Number 015300                                                                                                                                        | 2-16                             |

| SECTION 3 | Service Information                                                                                                                                                                 |                                  |

| 3.1       | Introduction                                                                                                                                                                        | 3-1                              |

| 3.2       | Calibration                                                                                                                                                                         | 3-1<br>3-1<br>3-2                |

| 3.3       | Test Equipment                                                                                                                                                                      | 3-2                              |

| 3.4       | Test Set-Up                                                                                                                                                                         | 3-3                              |

| 3.5       | Test Procedure                                                                                                                                                                      | 3-4                              |

| 3.6       | Trouble-Shooting                                                                                                                                                                    | 3-10                             |

| SECTION 4 | Model 8171 Options                                                                                                                                                                  |                                  |

|           | 4.1.0 Option 18 - Parallel BCD Output 4.1.1 Option 18 - Principles of Operation 4.1.2 Option 18 - Performance Checks                                                                | 4-1<br>4-2<br>4-3                |

|           | 4.2.0 Option 19 - Remote Output Driver 4.2.1 Option 19 - Specifications 4.2.2 Option 19 - Principles of Operation 4.2.3 Option 19 - Performance Checks                              | 4-4<br>4-5<br>4-6<br>4-7         |

|           | 4.3.0 Option 23 - IRIG B Output 4.3.1 Option 23 - Specifications 4.3.2 Option 23 - Internal Switches 4.3.3 Option 23 - Principles of Operation 4.3.4 Option 23 - Performance Checks | 4-8<br>4-8<br>4-9<br>4-9<br>4-10 |

#### CONTENTS

| SECTION 4 | Model 8171 Options (continued)                   | PAGE |

|-----------|--------------------------------------------------|------|

|           | 4.4.0 Option 24 and 25 - TCXO and External       |      |

|           | Oscillator Input                                 | 4-12 |

|           | 4.4.1 Option 24 and 25 - Specifications          | 4-12 |

|           | 4.4.2 Option 24 and 25 - Principles of Operation |      |

|           | 4.5.0 Option 30 - Fully Decoded Text Stream      | 4-13 |

|           | 4.5.1 Option 30 - Principles of Operation        | 4-14 |

|           | 4.5.2 Option 30 - Performance Checks             | 4-14 |

| SECTION 5 | REPLACEABLE PARTS LIST                           |      |

| SECTION 6 | MANUAL REVISIONS                                 |      |

|           |                                                  |      |

|           | ILLUSTRATIONS                                    |      |

| ť         |                                                  |      |

| FIGURES   |                                                  | PAGE |

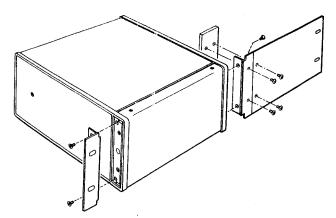

| 1-1       | Rack Mount (Option 01)                           | 1-3  |

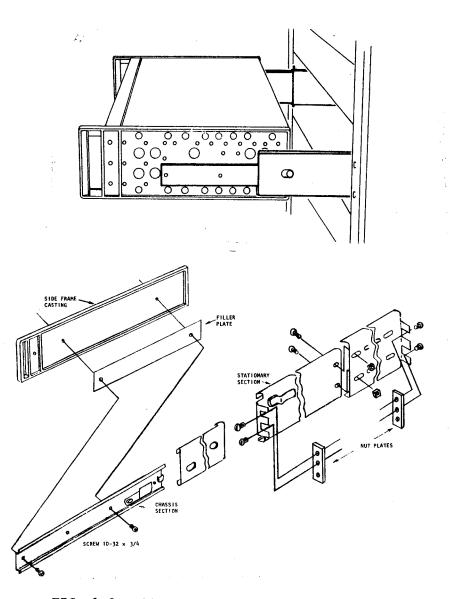

| 1-2       | Rack Mount with Slides (Option 11)               | 1-3  |

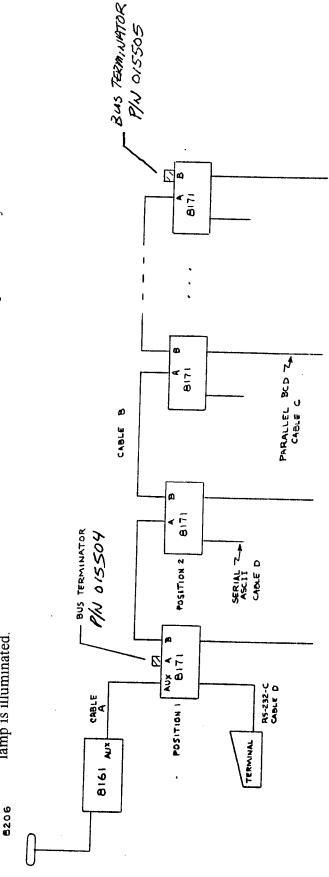

| 1-3       | System Configuration                             | 1-6  |

| 1-4       | Sample Memory Dump                               | 1-12 |

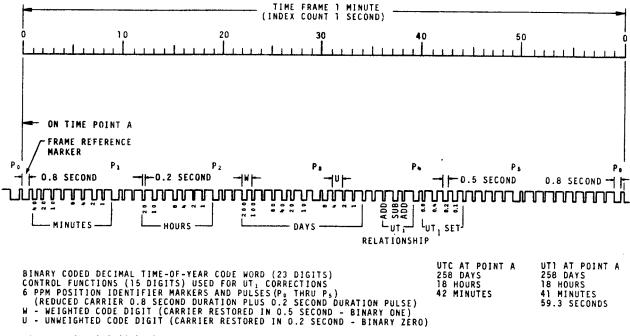

| 1-5       | WWVB Time Code Format                            | 1-14 |

| 1-6       | Path Delay Map                                   | 1-16 |

| 1–7       | AUX IN/OUT Connector                             | 1-18 |

Block Diagram, Microprocessor Assembly

Assembly Drawing - Microprocessor

Assembly Drawing, DC Power Supply

Remote Connector and Serial ASCII Connector

Schematic, Display Assembly

Schematic, DC Power Supply

Test Set-Up, Block Diagram

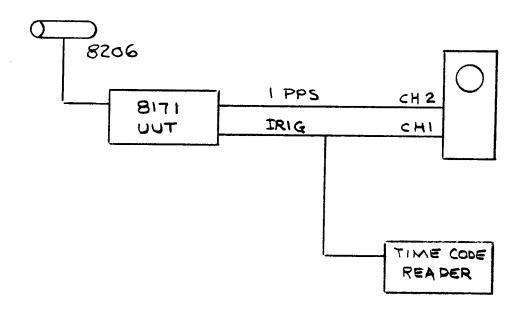

IRIG Test Set-Up

Assembly Drawing, Display Assembly

Schematic - Microprocessor Assembly - Sheet 1

1-20

2-2

2-3

2-4

2-5

2-6

2-7

2-8

2-9

2-10

2-11

2-14

2-15

2-16

2-17

3-3

4-4

4-11

- Sheet 2

- Sheet 3

- Sheet 4

- Sheet 5

- Sheet 6

- Sheet 7

- Sheet 8

1-8

2-1

2-2

2-3

2-4

2-5

2-6

2-7

3-1

4-1

4-2

Remote Connector

### SECTION 1

### 8171A

### INSTALLATION & OPERATION

- 1.1 Introduction

- 1.2 Installation

- 1.3 Operation

- 1.4 Specifications

#### 1.1 INTRODUCTION

The Spectracom Model 8171A Synchronized Clock decodes the time signal output of a Model 8160A, 8161, or 8164 WWVB Receiver/Frequency Standard, and provides a front panel display of hours, minutes, and seconds. A serial RS-232C interface provides on command: day of the year, hours, minutes, seconds, time zone and status information. A 1-Hz on-time pulse that signals the beginning of each second is available on the rear panel. A thumbwheel switch on the rear panel provides for time zone, daylight saving time, and path delay corrections. Several Model 8171 units may be "daisy-chained" together and connected to the output of a single WWVB Receiver/Frequency Standard.

Output data options include:

Option 18, Parallel BCD Output

Option 19, Remote Output (RS-422, RS-232). Option 19 is standard on units with serial numbers 8171-0566 and higher.

Option 23, IRIG B Output

Option 30, Fully Decoded Text Stream

Other options available are:

Option 01, Rack Mount Kit

Option 11, Rack Mount with Slides

Option 24, TCXO Stand-by oscillator

#### 1.2. INSTALLATION

#### 1.2.1 UNPACKING

In the event of damage to the shipping carton or if there is hidden damage inside but the carton is not damaged, be sure to contact the carrier immediately so that his representative can witness any equipment damage that may exist inside the carton. If you fail to report shipping damage immediately you may forfeit any claim against the carrier. You should also notify Spectracom Corporation of shipping damages so that we can assist you in obtaining a replacement or repair the equipment.

Be sure to remove all items of equipment and accessories from the shipping carton before discarding it. This includes a three-conductor line cord, an instruction manual, and an ancillary kit.

#### 1.2.2 RESHIPMENT

If it is necessary to return the unit to the factory, the original shipping carton may be used. If it is not available, a carton of at least 250# test corrugated paper with at least two inches of polyethylene foam surrounding the unit must be used. The unit should be sealed in a plastic bag for moisture protection and a note must be included stating the reason for the return.

#### 1.2.3 INPUT POWER

The equipment may be operated from 115 VAC  $\pm 10\%$ , 50/60-Hz line power.

#### 1.2.4 OPERATING ENVIRONMENT

The equipment is designed for operation in a room temperature laboratory environment. Operation outside a temperature range of 0 to 50°C may cause malfunction or damage to the equipment.

#### 1.2.5 BENCH OPERATION

The instrument is provided with four feet for standing on a benchtop surface, along with a tilt stand which may be used to provide a convenient viewing angle.

### 1.2.6 RACK MOUNT KIT (Option 01)

Units purchased with the rack mount kit are not provided with the tilt stand. The four mounting feet are included but these may be removed when the receiver is installed in a rack.

The rack mount panel extensions are installed by removing the vinyl-covered filler panels located just behind the handles on the sides of the enclosure. The rack mounting brackets are installed using the oval head  $\#10-32 \times 3/8$  screws provided. Truss head  $\#10-32 \times 3/8$  screws are furnished to mount the unit to the rack. (See Figure 1-1)

### 1.2.7 RACK MOUNT WITH SLIDES (Option 11)

The chassis section of the slides are attached to the sides of the receiver using the  $\#10-32 \times 3/4$  screws provided. The filler plates are located between the slides and the receiver sides.

The stationary section of each rack slide must be assembled to the proper length for the rack being used, using the brackets, screws, and nuts provided. The slides are bolted to the front and rear channels of the rack using the  $\#10-32 \times 1/2$  screws and nut plates as shown in Figure 1-2. Additional panel mounting angles (such as Emcor No. PMA) may be added to the rack cabinet for securing the front ends of the stationary slide sections if needed. They should be located immediately behind the panel mounting angles to which the equipment panel extensions will be fastened.

FIG. 1-1 RACK MOUNT OPTION 01

FIG. 1-2 RACK MOUNT WITH SLIDES (OPTION 11)

### 1.2.8 INTERNAL SWITCHES

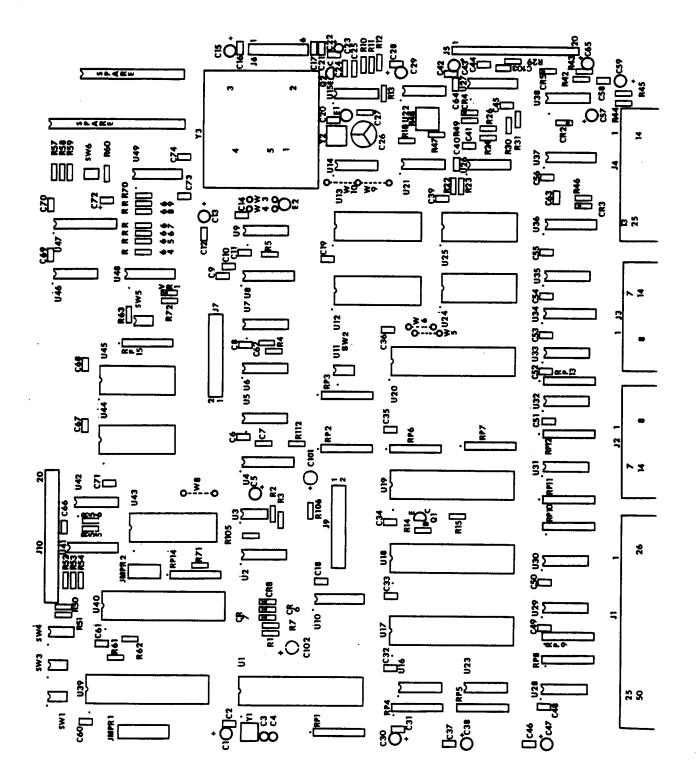

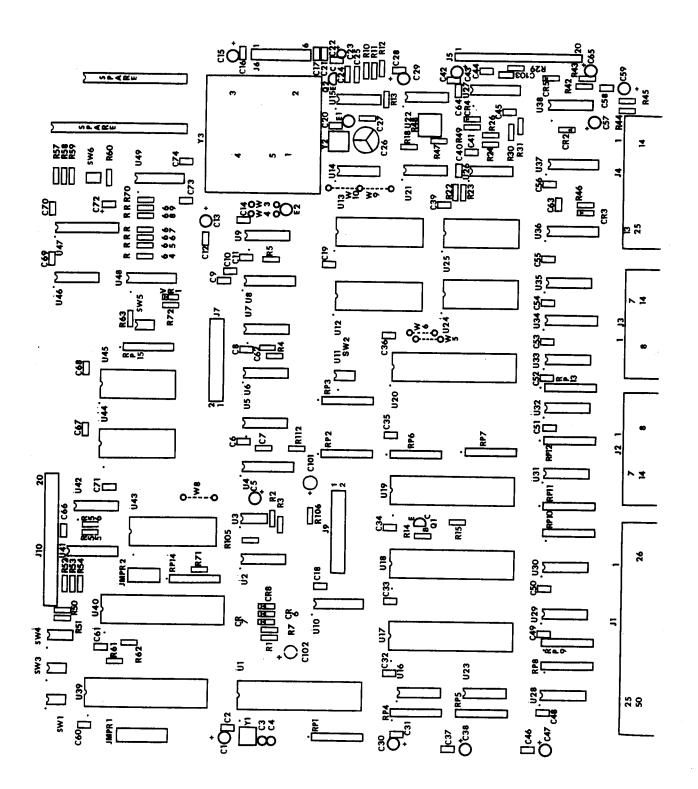

Refer to Figure 2-3 for physical location of internal switches.

The switch functions are listed below. The switch is present only if the Option is present.

| SW1   | Option 30 | Select year - units position |

|-------|-----------|------------------------------|

| SW2   | Standard  | Selectable Bit Rate          |

| sw3   | Option 30 | Select year - tens position  |

| SW4-1 | Option 23 | IRIG B Control Function      |

| -2    | Option 30 | Select Option 30             |

| -3    | Standard  | Time Sync LED Time Out       |

| -4    | Standard  | Time Sync LED Time Out       |

| SW5   | Option 23 | IRIG Code Select             |

| SW6   | Option 23 | IRIG TTL/AM Output Select    |

The standard unit contains the following switches. They are set at the factory to the positions indicated below:

| SWITCH | SET |   | DESCRIPTION                         |

|--------|-----|---|-------------------------------------|

| SW2    | 2   |   | Selectable Bit Rate set to 300 baud |

| SW4-1  | X   |   | X - don't care                      |

| -2     | OFF |   | Option 30 not present               |

| -3     | ON  | ) | Time Sync Time Out set              |

| -4     | ON  | ) | for 3 hours                         |

Switch (SW2) located on the microprocessor assembly A1A2 is a 10-position switch which controls the bit rate of the serial I/O port. The table below lists the bit rate as a function of the switch setting.

| Switch Position | Bit Rate |  |

|-----------------|----------|--|

| 0               | 75       |  |

| 1               | 150      |  |

| 2               | 300      |  |

| 3               | 600      |  |

| 4               | 1200     |  |

| 5               | 2400     |  |

| 6               | 4800     |  |

| 7               | 9600     |  |

| 8               | 19200    |  |

| 9               | 110      |  |

If Option 18 Parallel BCD and Option 23 IRIG B are present, then switch SW4-1 is set OFF (open) and data is sent out the parallel BCD connector.

If Option 23 IRIG B is present, then SW5 is set to position 2, IRIG B select and SW6 is set ON - TTL output.

If Option 30, Fully Decoded Text Stream is present, then SW3 and SW1 are set to the last two digits of the current year (i.e. 84).

Refer to Section 4.0 Options for a detailed description of switches associated with each system.

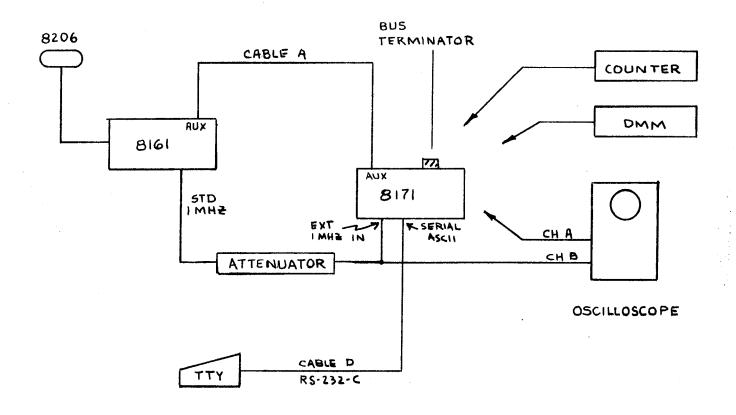

#### 1.2.9 CONNECTION AS PART OF A SYSTEM

The Model 8171A Synchronized Clock is driven by the time code output (Option 05) of a Model 8160A, 8161, or 8164. Figure 1-3, System Configuration, illustrates how several Synchronized Clock units may be connected in a "daisy-chain" to one receiver output. The AUX IN/OUT connector on the rear panel of the Receiver is connected by means of Cable A to the AUX connector on the rear panel of the first synchronized clock in the chain. Additional synchronized clocks are connected into the system using a Cable B from the Bus B connector on the rear panel of each synchronized clock to the Bus A connector on the next unit in the chain. The last unit in the chain must have a Bus Terminator connected to its Bus B connector. Similarly, the first unit must have a terminator connected to its Bus A connector. Cable B has a female connector for mating with the Bus B connector on the synchronized clock and a male connector for mating with the Bus A connector. Consequently, if a synchronized clock is removed from the chain, the two Cable B's connected to it may be connected to each other.

bus as shown in figure 1-3 below. Terminating the cable ends preserves data integrity by Note: A bus terminator assembly is required at each end of the RS-422 time distribution preventing signal reflections and oscillations.

terminator is required even if only one Model 8171A unit is utilized. If additional Model 8171A units are to be daisy-chained to the first 8171A unit's bus, connect the Bus B Terminate the Bus A connector with Bus Terminator part number 015504. This terminator part number 015505 to the last Model 8171A in the chain.

the chain to display and output the incorrect time even though the front panel Time Sync Failing to terminate the RS-422 time data bus may cause one or all the Model 8171A in lamp is illuminated.

FIG. 1-3 SYSTEM CONFIGURATION

# 1.2.10 MATING CONNECTORS & CABLES AND TERMINATORS

The mating connectors for the rear panel are listed below. The pin numbers for each signal are listed in Paragraph 1.4.3 of this section. Equivalent connectors may be substituted.

| REFERENCE                    | DESIGNATION                                          | MFR. PART NO.                               |

|------------------------------|------------------------------------------------------|---------------------------------------------|

| AUX IN/OUT                   | Plug, 15 Circuits<br>Pin                             | Molex 03-09-2151<br>Molex 02-09-2118        |

| Serial ASCII                 | Plug, 25 Circuits<br>Pin for 24-28 AWG wire<br>Shell | AMP 205208-1<br>AMP 66507-8<br>AMP 206478-3 |

| Bus B                        | Receptacle, 14 Circuits<br>Strain Relief Cover       | AMP 552312-1<br>AMP 2-552079-1              |

| Bus A                        | Plug, 14 Circuits<br>Strain Relief Cover             | AMP 552282-2<br>AMP 2-552079-1              |

| Parallel BCD                 | Plug, 50 Circuits<br>Strain Relief Cover             | AMP 229974-1<br>AMP 4-552008-1              |

| Remote Output<br>(Option 19) | Plug, 9 position<br>*Socket Pins<br>Shell            | AMP 205204-1<br>AMP 66506-8<br>AMP 206478-1 |

<sup>\*</sup> The crimping tool for the pins is AMP 90302-1. The insertion/extractor tool is AMP 91067-2.

# Cable assemblies and bus terminators are listed below:

| CABLE A    | Cable with male Molex connector at each end. Cable consists of three coaxial cables.                 | Spectracom CA06XXX<br>(XXX = cable length) |

|------------|------------------------------------------------------------------------------------------------------|--------------------------------------------|

| CABLE B    | RS-422 cable with 14-pin male Champ connector at one end and 14-pin female Champ connector at other. | Spectracom CA07XXX (XXX = cable length)    |

| TERMINATOR | 120-ohm Bus terminator housed in 14-pin Champ connector plug housing. Plugs into Bus A.              | Spectracom 015504                          |

| TERMINATOR | 120-ohm Bus terminator housed in 14-pin Champ connector receptacle housing. Plugs into Bus B.        | Spectracom 015505                          |

### 1.3 OPERATION

### 1.3.1 FRONT PANEL FUNCTIONS

Time Sync: The green lamp is turned on when the time code is fully decoded. In order to select the length of time before the time sync lamp goes out after loss of phase lock, switch (SW4-3,4) can be set to select 1 of 4 times:

| SW4-4   | SW4-3   |            | Typical      |

|---------|---------|------------|--------------|

| Setting | Setting | Time (min) | Error (msec) |

| 0       | 0       | 10         | 1            |

| 0       | 1       | 20         | 10           |

| 1       | 0       | 60         | 30           |

| 1       | 1       | 180        | 100          |

The lamp will come back on after the receiver reacquires phase lock to the WWVB carrier and the time code is decoded.

If high accuracy during loss of signal is required then Option 24 TCXO and External Oscillator is recommended. Refer to Section 4 - Options for details.

Display: The display initially indicates time since "power on" in the four right hand digits. After the Receiver/Frequency Standard acquires phase lock the sixth (left most) digit displays the code received. (See Figure 1-5, WWVB Time Code Format). A zero (0) is a logical zero, a one (1) is a logical one, a two (2) is a position identifier and a four (4) indicates a bit error. After the code is successfully received universal coordinated time (UTC) minus the time zone switch setting is displayed.

### 1.3.2 REAR PANEL FUNCTIONS

Thumbwheel Switch: This is a 5-digit switch. The right two digits are TIME ZONE. The left three digits are PROPAGATION DELAY and RECEIVER DELAY inputs. The propagation delay can be calculated (see Section 1.3.8 PROPAGATION PATH DELAY). The receiver delay is nominally 17 milliseconds. Set the switch to the sum of the path delay and receiver delay.

Daylight Savings Time: Use the TIME ZONE switch to adjust the display for local time.

Parallel BCD: Option 18 provides the day of the year, hours, minutes, seconds, time zone and status data on a 50-pin connector.

Remote Output Driver: Option 19 provides a RS-422 serial data output for driving Model 8172 Synchronized Wall Clocks or Model 8173 Multiple RS-232C Taps.

IRIG B Output: Option 23 provides 1-KHz carrier, amplitude modulated at 100 pps with time code or 100 pps DC level shift.

External Oscillator Input: Option 24 rear panel BNC input for 1.0-MHz standby clock oscillator.

Serial ASCII: This interface is a serial RS-232C port. The connector is a 25-pin series D socket.

There are 3 commands:

- S Set the clock

- T Read the time

- D Dump the memory

Power: International Electrotechnical Commission (IEC) male line cord receptacle.

Line Fuse: AC line fuse. AGC 3/4 A.

AUX: Input signal connector provides Receiver/Frequency Standard output signals to the first Model 8171 Synchronized Clock in the chain.

BUS A: Input signal connector provides inputs to Synchronized Clock units other than the first in the chain. A bus terminator is connected to the BUS A connector on the first unit of the chain.

BUS B: Output signal connector provides Receiver/Frequency Standard signals to the next Synchronized Clock in the chain. A bus terminator is connected to the BUS B connector on the last unit of the chain.

### 1.3.3 INITIAL TURN-ON

After the Model 8171A Synchronized Clock has been connected into the system as described above, plug it into the power line. The Model 8164, 8161 or 8160A Receiver should be turned on and operating. The Synchronized Clock will display the time since it was turned on in minutes and seconds. After the Receiver achieves phase lock the received time code will be displayed in the left-most significant digit position, as received at one bit per second.

The time code displayed in the left digit is coded:

- 0 binary zero

- 1 binary one

- 2 position identifier

- 4 bit error

The clock receives the code and sets itself automatically. The time it takes to set is dependent on the quality of the signal received. The quality of the signal is indicated by the code received. If many 4's are displayed, then the signal is poor. If the signal is good, then the clock will set in a few minutes. If there is a weak or noisy signal, it will take longer to set.

#### 1.3.4 COMMANDS

Commands are accepted through the Serial ASCII port. Commands are:

- T print the Time

- $S \underline{S}et$  the time

- $D \underline{D}ump$  the memory

Commands are not echoed back.  $\underline{\text{Do}}$  not enter Return after the command.

Serial Data Interface:

RS-232 Port: Standard in all units, provides day and time in response to a "T" input command. "S" command allows operator to set clock via a data terminal keyboard. "D" command causes a memory dump of statistical data for performance evaluation. A character consists of 1 start, 8 data, and 2 stop bits. Data rate is selectable from 300 to 19,200 baud.

Serial Data Structure: Response to a "T" command is:

(CR)(LF)I(SPACE)(SPACE)DDD(SPACE)HH:MM:SS(SPACE)(SPACE)TZ=XX(CR)(LF)

#### where:

- I = space if clock set by WWVB (TIME SYNC lamp on)

- \* if clock set manually via RS-232 port

- ? if time sync lamp is off

DDD = day of the year

HH:MM:SS = hours:minutes:seconds

XX = time zone switch setting at rear panel

Output is in UTC minus the time zone switch setting.

Option 30 Fully Decoded Text Stream: This alternate data format can be furnished when the unit is purchased:

(CR)(LF)I(SPACE)WWW(SPACE)DDMMMYY(SPACE)HH:MM:SS(CR)(LF)

where: I = as defined above

WWW =day of week (MON, TUE, WED, etc.)

DD = numeric day of month (01 to 31)

MMM = month (JAN, FEB, MAR, APR, etc.)

YY = year without century (83, 84, 85, etc.)

HH:MM:SS = as defined above.

"S" Command - to manually set the clock, enter:

**SDDDHHMMSS**

where: S = set command

DDD = UTC day of year

HH = UTC hours

MM = minutes

SS = seconds

Entry of the last seconds digit sets the clock to UTC time minus the time zone switch settings. The WWVB-derived on-time pulse increments the clock every second. If phase lock to the carrier has been acquired, the on-time second pulses are phase locked to the time code pulses even though the unit may temporarily be unable to decode the incoming signal. Thus, if the manual setting started the clock within one second after the correct on-time pulse, it will run truly on-time, as though it had set itself.

If Option 30 is present and the operator enters 366 for DDD day and the internal year switch is not set to a leap year, then the error message "\*CHK YEAR SW" will be printed.

"D" Command - the "dump the memory" command, will print the contents of the 256-byte RAM memory. Performance event counters stored in RAM are:

Phase Lock Lost Counter PLLC

Time Code Compare Counter TCCC

The print out represents physical address locations 0800 through 08FF. The data is printed in hexadecimal notation. PLLC is a two-byte counter whose contents are printed at row 0810, columns 8 and 9. The first byte is the least significant byte. The counter records the number of times phase lock has been lost since power-on.

The Time Code Compare Counter, TCCC, records the number of times the received data compares with the expected value. It is printed at row 0820, columns 8 and 9. It is a 2-byte hexadecimal number printed least significant byte first.

```

PLLC

TCCC

Pointer to phase

1 2 3 4 5 6

9 A B / C D E

adjust table

DO 48 00 1D 02 DO E9 F4 00 10 00 FF 14 A3 08 FF

0800

0810

00 FF 00 01 00 00 F4 00 00 00 45/54 00 FF 00 00

0820

00 27 28 14 25 05 00 01 99 07 01 00 00 00 99 49

0830

29 28 14 25 00 00 00 03 01 28 FF 34 48 00 00 00

0840

42 31 28 14 02 50 50 00 00 32 28 14 25 05 00 00

0850

30 30 20 20 20 32 35 30 20 31 34 3A 32 38 3A 32

0860

33 20 20 54 5A 3D 30 30 QD 0A 00 0Q 53 48 00 00

0870

0880

80 48 7D 00 UC 44 00 00 FF FF FF FF 00 00 00 00

Time Flags

0890

0880

06 13 00 15 20 00 15 50 FF 19 04 FF 22 00 FF 00

08B0

00 FF 01 53 00 02 15 00 02 46 00 03 13 00 03 54

0800

00 04 48 00 09 51 00 10 39 00 11 12 00 14 39 FF$

Phase Adjust Table

08D0

17 U3 FF 20 35 FF 04 25 00 09 12 00 20 52 FF 0Q

08E0

00 00 00 00 00 00 00 00 00 03 43 B4 45 EA 47 F2

08F0

41 88 47 00 49 00 00 00 00 54 64 04 41 00 00 00

```

FIGURE 1-4 SAMPLE MEMORY DUMP

#### 1.3.5 PHASE ADJUST TABLE

The 1 PPS on-time pulse is phase locked to the leading edge of the received time code signal. After the initial turn-on sequence the phase adjustments are in 0.1 millisecond increments. Each time an adjustment is made the time and direction of the adjustment are logged in a circular table. The table is located at 08A0 through 08DE. The table contains the data on the last 21 phase adjustments. UTC hours and minutes followed by 00 or FF are logged, where 00 indicates the 1 PPS was shifted 0.1 millisecond left (early) and FF indicates that the 1 PPS was shifted 0.1 millisecond right (late). The current position pointer is located at row 0800, columns D and E, least significant byte first. This points to the memory location where the next adjustment will be stored.

After the unit has been on a few days the adjustment interval will exceed 24 hours. If adjustment data is desired the memory should be dumped at least once every 24 hours. This eliminates ambiguity concerning which day the adjustment was made.

#### 1.3.6 TIME FLAGS

At power-on or after the signal has been lost for longer than 180 minutes (depending on the setting of SW4-3,4) the Time Sync light will be off. This indicates that the time may be in error by greater than 100 milliseconds. The Time Sync light is turned on when a good time code is received. A received time code must pass a number of tests. When the seconds, minutes, hours and days portion of the time code are acceptable, flags are set to FF at row 0880, columns 8 through C. The clock is set and the Time Sync light is turned on when all the flags are set. This data is useful during the initial installation and trouble shooting to determine the progress of the self-setting process. When all the flags are set the TCCC is incremented, the flags cleared, and the process is repeated.

Once the Time Sync light is on the clock will keep UTC time. The display will be changed when 3 consecutive good compares are received that do not agree with the display data. This will happen when the leap second is inserted at the NBS WWVB transmitter.

#### 1.3.7 TIME CODE FORMAT

The WWVB time code is generated at the transmitter by a 10-dB reduction of the carrier power of 10 dB at the beginning of each second. It is restored to a full power 200 milliseconds later for a binary zero, 500 milliseconds later for a binary one, and 800 milliseconds later for a position identifier. Decoding a one-minute data stream yields day of the year, time of day, and a correction factor for converting from atomic time (Coordinated Universal time, UTC) to earth time (UT1). Figure 1-5 WWVB TIME CODE FORMAT shows the coded data in a 1-minute time frame.

NOTE: BEGINNING OF PULSE IS REPRESENTED BY NEGATIVE - GOING EDGE.

9/75

#### FIGURE 1-5 WWVB TIME CODE FORMAT

#### 1.3.8 PROPAGATION PATH DELAY

Radio waves at low frequencies use the earth and the ionosphere as a waveguide and follow the earth's curvature for long distances. To compute the propagation path delay the great circle distance between the two points is divided by the speed of light.

The approximate formula for finding the great circle distance from Ft. Collins, Colorado, to another point in the northern hemisphere is given below. The error is 2% or less.

Distance =  $60 \cos^{-1}$  (.758 cos (LAT) cos (P) + .652 sin (LAT)) nautical miles.

where: LAT = latitude of receiver

P = (Longitude of WWVB) - (longitude of receiver)

WWVB is at 105°02' 39.5" W longitude The speed of light is 300 Km/millisecond

To convert from nautical miles to millisecond delay:

PATH DELAY = Nautical Miles x 1.8522 Km/Nautical mile 300 Km/msec An example of the calculation is given below for Boston:

### PATH DELAY = 1521 nautical miles x 1.8522 Km/nautical mile 300 Km/msec

#### = 9.4 milliseconds

The path delay from the WWVB transmitter in Ft. Collins, Colorado, to Boston is 9.4 milliseconds.

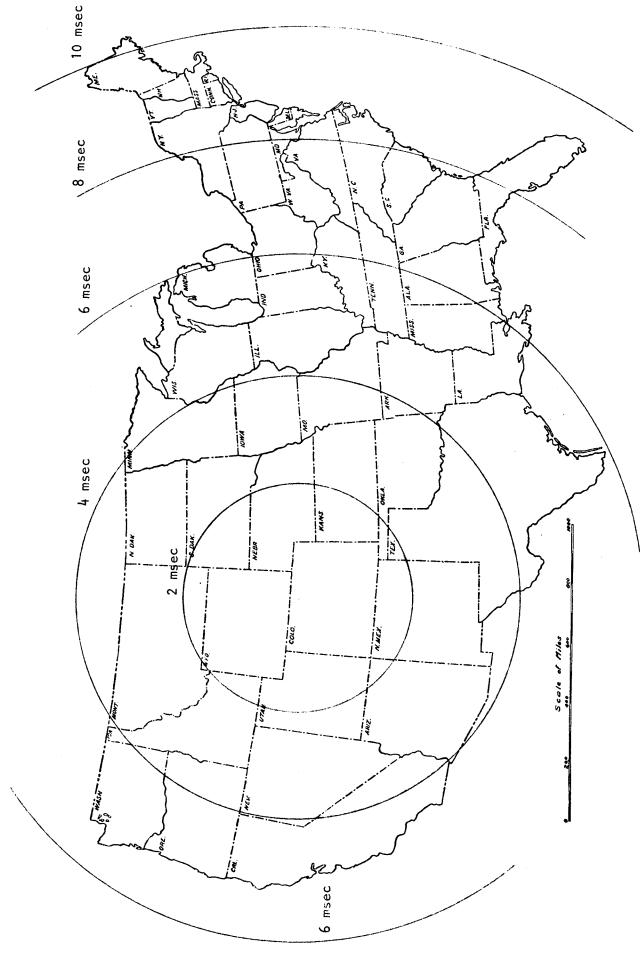

Figure 1-6 Path Delay Map shows the United States with concentric circles around Ft. Collins, Colorado. The radius of the inner circle is 600 Km and represents a 2 millisecond path delay. Outer circles represent increasing 2 millisecond delays. The map provides only an approximate value for path delay.

FIG. 1-6 PATH DELAY MAP

### 1.4 SPECIFICATIONS

### 1.4.1 MECHANICAL & INSTALLATION

Size: 3.5H x 13D x 17W (inches). Height is 4.25 inches including feet. If feet are removed, unit may be mounted in a 3 1/2" rack space.

$88.9H \times 330.2D \times 431.8W$  (mm). Height is 107.9 mm including feet.

Handles protrude 1.75 inches (45mm) from front panel.

Allow 2-3 inches cable clearance at rear.

Weight: 13 lbs. (5.9 Kg): Shipping Wt. 16 lbs. (7.26 Kg).

Line Power: 115/230 VAC ±10%, 50/60 Hz, 0.2 Amps.

Operating Temperature: 0 to 50°C.

#### 1.4.2 TIME ACCURACY

Ultimate Accuracy: ±0.1 msec

Overall Accuracy: ±(0.1 msec + noise uncertainty + propagation and receiver delay calibration error)

Noise Uncertainty: Less than ±0.5 msec when atomospheric signalto-noise ratio is -10 dB in a 1.0 KHz bandwidth at the antenna (expected summertime worst case in U. S. coastal areas.)

Short-term jitter: 1.0-Hz on-time pulses are phase locked to the received time code and to the WWVB carrier and phase-corrected in 0.1-msec steps. The correction interval varies from about 1 hour to several days. The typical peak-to-peak jitter is less than 2 microseconds.

### 1.4.3 AUX IN/OUT

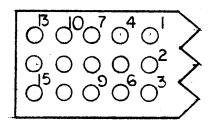

The AUX IN/OUT connector on the rear panel is the interface connector to the Model 8160A, 8161, or 8164. The connector is a 15-pin Molex connector (R03-09-1151.) Figure 1-7 shows the connector as viewed from the rear of the unit.

FIGURE 1-7 AUX IN/OUT CONNECTOR

Interface signals and pin assignments are listed below:

| SIGNAL            | PIN |

|-------------------|-----|

| 10 MHz            | 13  |

| 10 MHz Shield     | 14  |

| Phase Lock        | 5   |

| Time Code         | 7   |

| Time Code Shield/ |     |

| Phase Lock Shield | 4   |

| Enable            | 9   |

| Inhibit           | 12  |

The signal functions and specifications are:

10 MHz: Phase locked to the WWVB carrier, 3.4V rectangular pulse into 100 ohms. TTL-compatible.

Phase Lock: Indicates when receiver output is phase locked to the WWVB carrier. Ground level when unlocked, +5 VDC behind 3.3K ohms when locked.

Time Code: BCD time code yielding date and time of day. Logic high is +5 VDC behind 3.3K ohms, low is ground.

Enable: +5 Volts behind 100 ohms. Jumpered to INHIBIT signal in cable. Enables tri-state RS-422 driver.

Inhibit: Input impedance is 1000 ohms to ground. Connected to control input of RS-422 driver.

#### 1.4.4 1 PPS ON-TIME OUTPUT

A positive-going signal phase locked to the leading edge of the WWVB 10-dB power reduction. The signal has a 10% duty factor and is TTL-compatible. BNC connector.

### 1.4.5 1-MHZ STANDBY INPUT

This signal is AC coupled into a 100-ohm terminating resistor. The signal level must be a minimum of 1 V peak-to-peak and a maximum of 10 V peak-to-peak. A BNC connector is used.

#### 1.4.6 IRIG OUTPUT

If Option 23, IRIG B is present, then the Serial IRIG signal is brought out on this connector. The type of signal is selected internally by SW6.

SW6 ON TTL 50-ohm line driver output signal.

SW6 OFF A 1-KHz amplitude modulated sine wave. The open circuit output signal is nominally 8 volts peak-to-peak for a MARK and 2.4 volts peak-to-peak for a space. The output impedance is 50 ohms. It will drive a 600-ohm or greater load.

### 1.4.7 366/365 SWITCH

This leap year switch insures proper roll-over on day 366 and roll-back on day 1.

### 1.4.8 TIME ZONE SWITCH

This is a two-digit thumbwheel switch with a range of 00 to 19. The time displayed is UTC time received less the thumbwheel switch setting.

#### 1.4.9 PATH DELAY SWITCH

This is a three-digit thumbwheel switch used to correct for propagation delay of the signal from Ft. Collins, Colorado, and receiver delay. Range is 00.0 to 99.9 milliseconds.

#### 1.4.10 REMOTE OUTPUT CONNECTOR - OPTION 19

The Option 19 Remote Output Connector is a 9-pin series D receptacle (female). Figure 1-8 shows the pin locations viewed from the rear of the Model 8171. Option 19 is standard on units with serial numbers 8171-0566 and higher.

FIGURE 1-8 REMOTE CONNECTOR

| SIGNAL                      | MNEMONIC               | REMOTE CONNECTOR_PIN | SERIAL ASCII<br>CONNECTOR_PIN |

|-----------------------------|------------------------|----------------------|-------------------------------|

| BUS DATA<br>BUS DATA        | -BDATA<br>+BDATA       | J11-3<br>-8          |                               |

| BUS ON-TIME<br>BUS ON-TIME  | -BON-TIME<br>+BON-TIME | J11-2<br>-7          |                               |

| BUS TIME SYNC BUS TIME SYNC | -BTSYNC<br>+BTSYNC     | J11-1<br>-6          |                               |

| ENABLE                      | ENABLE                 | J11-4                |                               |

| GROUND TIME DATA            | GND<br>TDATA           | -9<br>J11-5          | J11-19                        |

BDATA, BON-TIME and BTSYNC signals conform to EIA RS-422 standard. TDATA conforms to RS-232C signal levels.

The +BON-TIME signal is a positive-going 0.1-second pulse relative to -BON-TIME, occurring once per second. The leading edge of the pulse is the beginning of the second.

The +BTSYNC signal is high relative to -BTSYNC after the NBS time code has been decoded. The signal goes lown minutes after the receiver has lost phase lock with the NBS signal. The number of minutes, n, that the signal stays active after the receiver has lost phase lock is selected by switch AlA2 SW4-3,4. It remains low until another successful decoding is accomplished.

The ENABLE signal is +5 volts in series with 60 ohms.

#### 1.4.11 SERIAL ASCII

The Serial ASCII port provides the day and time data in ASCII format. The interface is RS-232 compatible. The connector is a 25-pin series D female connector. The signal and pin numbers are listed below.

| <u>SIGNAL</u>                 | MNEMONIC | PIN                |

|-------------------------------|----------|--------------------|

| Protective Ground             | AA       | J <del>4-1</del>   |

| Transmit Data                 | BA       | J4-2 (IN TO 8171)  |

| Receive Data                  | BB       | J4-3 (OUT OF 8171) |

| Clear-to-send                 | СВ       | J4-5               |

| Data Set Ready                | CC       | J4-6               |

| Signal Ground                 | AB       | J4-7               |

| Received Line Signal Detector | CF       | J4-8               |

The Clear-to-Send signal is connected to +12 VDC through a 5.6K resistor. The Received Line Signal Detector and Data Set Ready will be high when power is on, and are connected together and tied to +12 volts through a 5.6K resistor.

The time data is sent out in response to a "T" command. The data represents the time at the <u>beginning</u> of the first character sent. The bit rate is selectable by switch AlA2 SW2. Refer to Section 1.2.8 Internal Switches for information on bit rate selection.

Relative to RS-232 definitions, the Model 8171 is a data communication equipment DCE. Transmit Data, BA, is  $\underline{to}$  the Model 8171. Received Data, BB, is  $\underline{from}$  the Model 8171.

### 1.4.12 BUS B

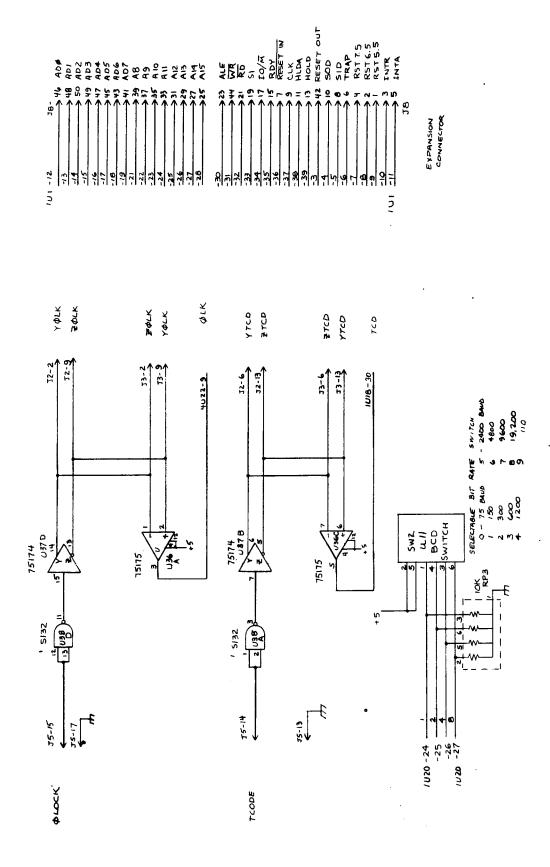

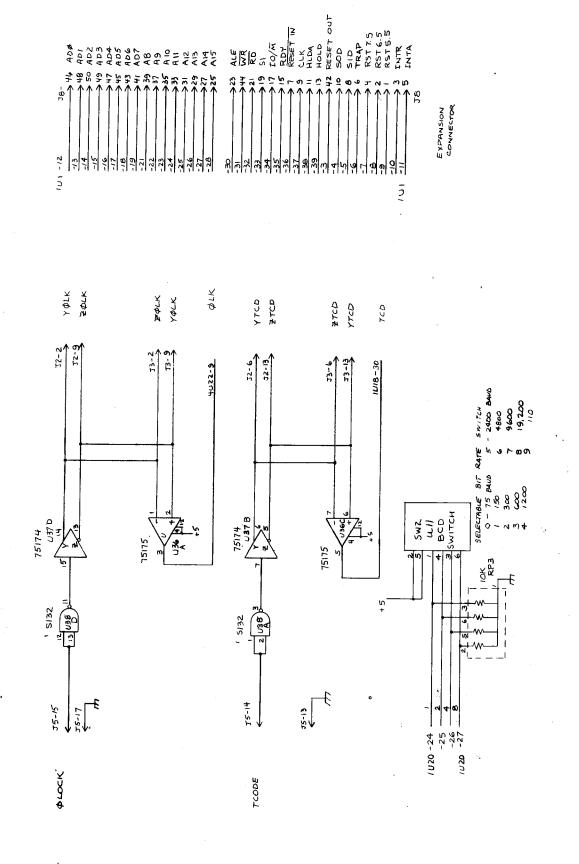

BUS B is an RS-422 bus. The connector is a 14-pin plug, AMP CHAMP part 552739-1 or equivalent. The signals and pin assignments are listed below:

| SIGNAL | MNEMONIC | PIN |

|--------|----------|-----|

| +1 MHZ | Ylmhz    | 5   |

| -1 MHZ | ZIMHZ    | 12  |

| +ØLOCK | YØLK     | 2   |

| -ØLOCK | ZØLK     | 9   |

| +TCODE | YTCD     | 6   |

| -TCODE | ZTCD     | 13  |

| GND    | GND      | 1   |

| GND    | GND      | 8   |

Pin reference numbers are on the connector.

#### 1.4.13 BUS A

BUS A is an extension of BUS B. The BUS B signals appear on corresponding pins on BUS A. The connector is a 14-pin receptacle, AMP CHAMP part 552738-1 or equivalent.

#### 1.4.14 PARALLEL BCD - OPTION 18

The Parallel BCD Output option provides day and time data in Parallel BCD format on a 50-pin connector. All lines are TTL-compatible.

Data is valid from 20 milliseconds before the ON-TIME pulse until 850 milliseconds after the ON-TIME pulse. Signals are positive logic, i.e. a logical 1 is high, a logical 0 is low.

There will be no data out until the clock has been set by WWVB or by the manual SET command.

#### 1.4.15 TIME SYNC - FRONT PANEL LED

The green lamp is turned on when the time code is fully decoded. In order to select the length of time before the time sync lamp goes out after loss of phase lock, switch (SW4-3,4) can be set to select 1 of 4 times:

| SW4-4   | SW4-3   |            | Typical      |  |

|---------|---------|------------|--------------|--|

| Setting | Setting | Time (min) | Error (msec) |  |

| 0       | 0       | 10         | 1            |  |

| 0       | 1       | 20         | 10           |  |

| 1       | 0       | 60         | 30           |  |

| 1       | 1       | 180        | 100          |  |

The lamp will come back on after the receiver reacquires phase lock to the WWVB carrier and the time code is decoded.

#### 1.4.16 STAND-BY CRYSTAL OSCILLATOR

Temperature Stability 20°C to 30°C:  $\pm 1 \times 10^{-6}$ /°C

Aging Rate:  $2 \times 10^{-6}$  for first 6 months,  $2 \times 10^{-6}$ /year thereafter.

Frequency Adjustment: Sufficient to compensate for 10 years of aging.

Adjustment Resolution,  $1 \times 10^{-7}$

Accuracy: Set at the factory to  $\pm 1 \times 10^{-6}$

### 1.4.17 SELECTABLE BIT RATE

The Serial ASCII output is internally switch-selectable to 75, 150, 300, 600, 1200, 2400, 9600, 19,200, and 110 bits per second by switch A2Al SW2 located in position marked Ull. Refer to Section 1.2.8 for bit rate select table.

#### 1.4.18 OPTIONS IN NUMERICAL ORDER

Option 01: Rack Mount Kit

Option 11: Rack Mount with Slides

Option 18: Parallel BCD

Option 19: Remote Output Driver (standard on all units with

serial numbers 8171-0566 and higher)

Option 23: IRIG B Output

Option 24: TCXO (Temperature Controlled Crystal Oscillator)

Option 30: Fully Decoded Text Stream

# SECTION 2

# 8171A

### THEORY OF OPERATION

- 2.1 Introduction

- 2.2 Microprocessor Assembly

- 2.3 Display Assembly

- 2.4 DC Power Supply Assembly

#### 2.1 INTRODUCTION

The 8171A Synchronized Clock consists of a Microprocessor Assembly, a Display Assembly, and a Power Supply Assembly, as shown in Figure 2-1 Block Diagram, Microprocessor Assembly.

The phase-locked 10 MHz, phase lock condition signal, and detected time code outputs of the Model 8160A, 8161, or 8164 Receiver are fed into the input of the microprocessor. In addition to the front panel display, day and time data are supplied in ASCII format via the RS-232 interface on the rear panel.

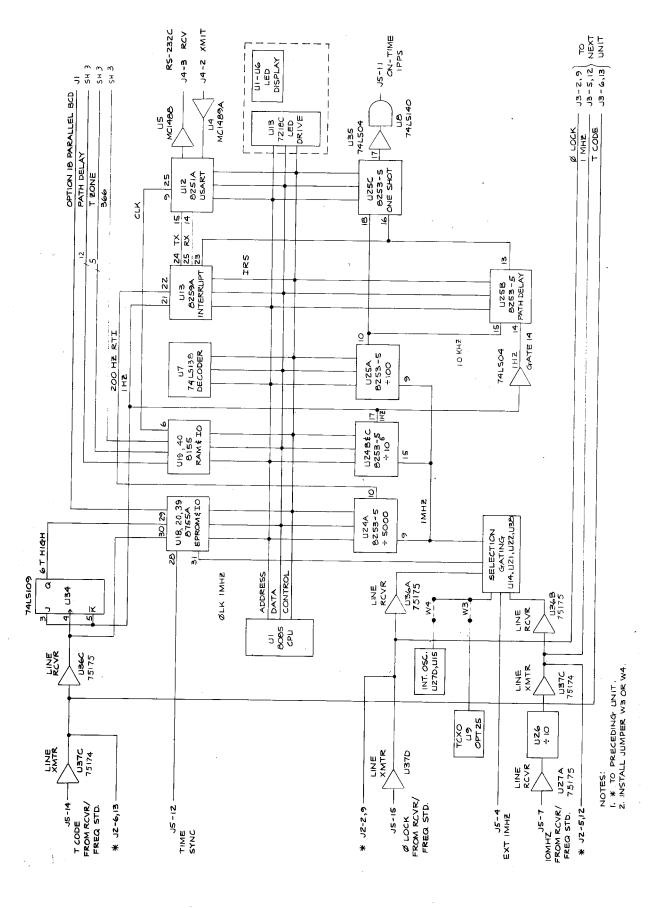

The Microprocessor Assembly consists of an 8085A microprocessor, 6K of EPROM, 512 bytes of RAM, 2 timer chips, a priority interrupt controller, a USART, RS-422 receivers and transmitters, and an LED display interface.

The processor integrates out the noise, measures the time code pulse widths, decodes the signal, phase locks a 1-Hz on-time pulse to the WWVB input signal, and controls the display and time-of-year outputs.

Input signals from the thumbwheel switch on the rear panel provide time zone and path delay corrections.

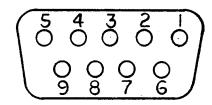

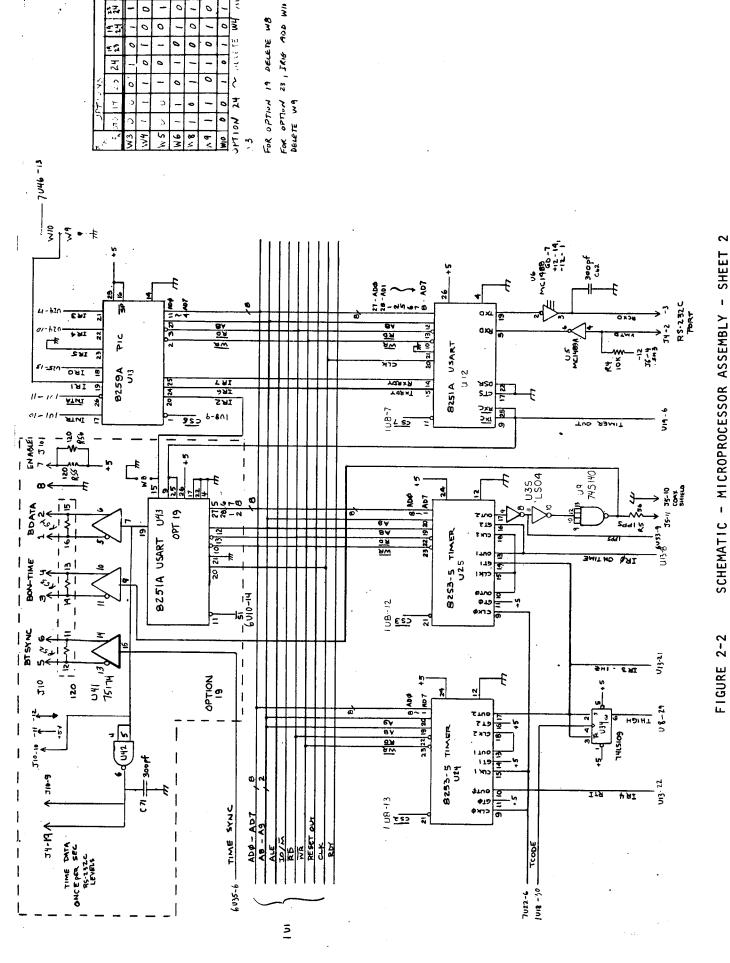

### 2.2 MICROPROCESSOR ASSEMBLY, A1A2, P/N 015500

The Microprocessor Assembly decodes the WWVB time code signal output of the Receiver/Frequency Standard and compensates for propagation and receiver delays and for time zone differences. The time of day is displayed on the front panel. The day and time data are provided to the ASCII interface on the rear panel. An optional parallel BCD output of this information is also available.

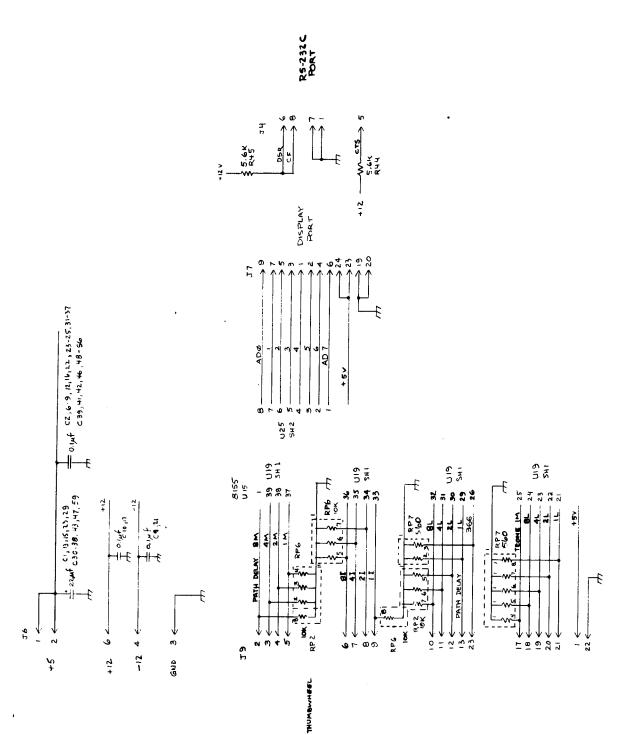

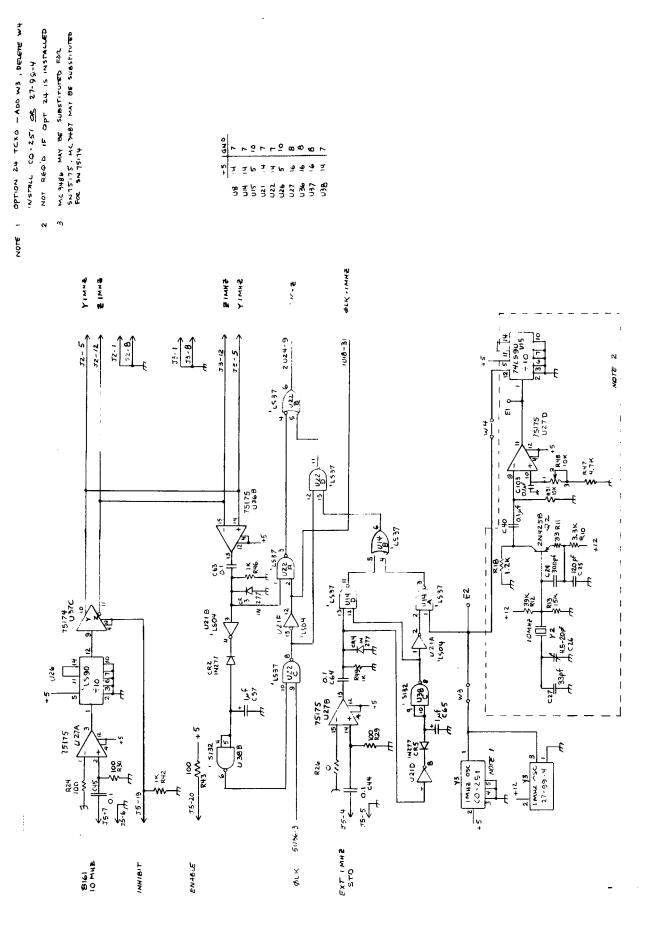

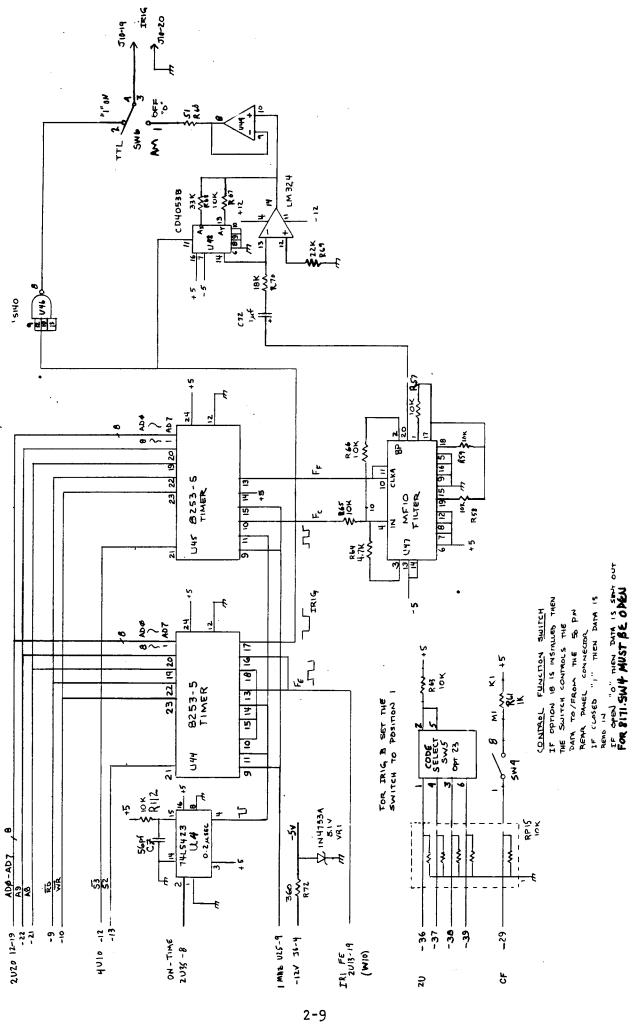

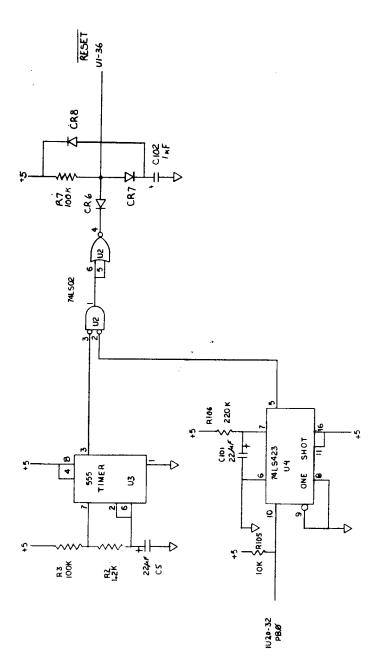

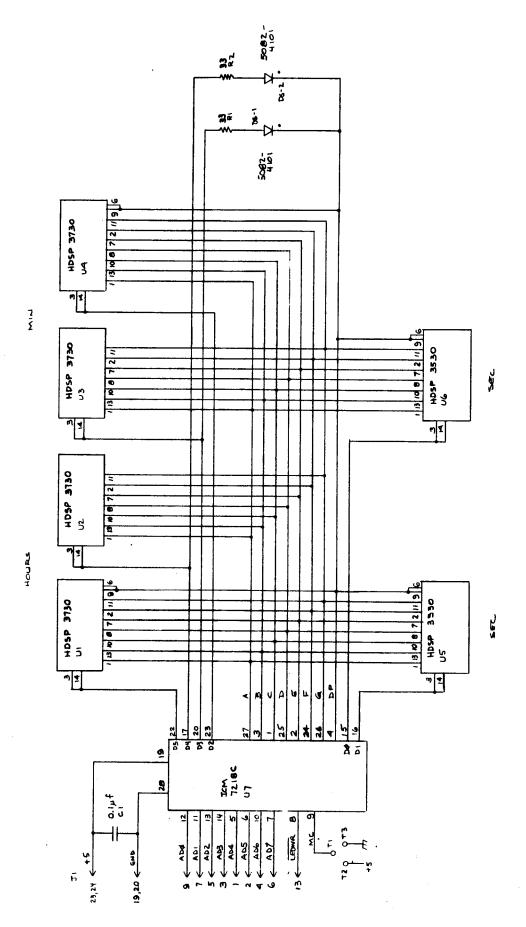

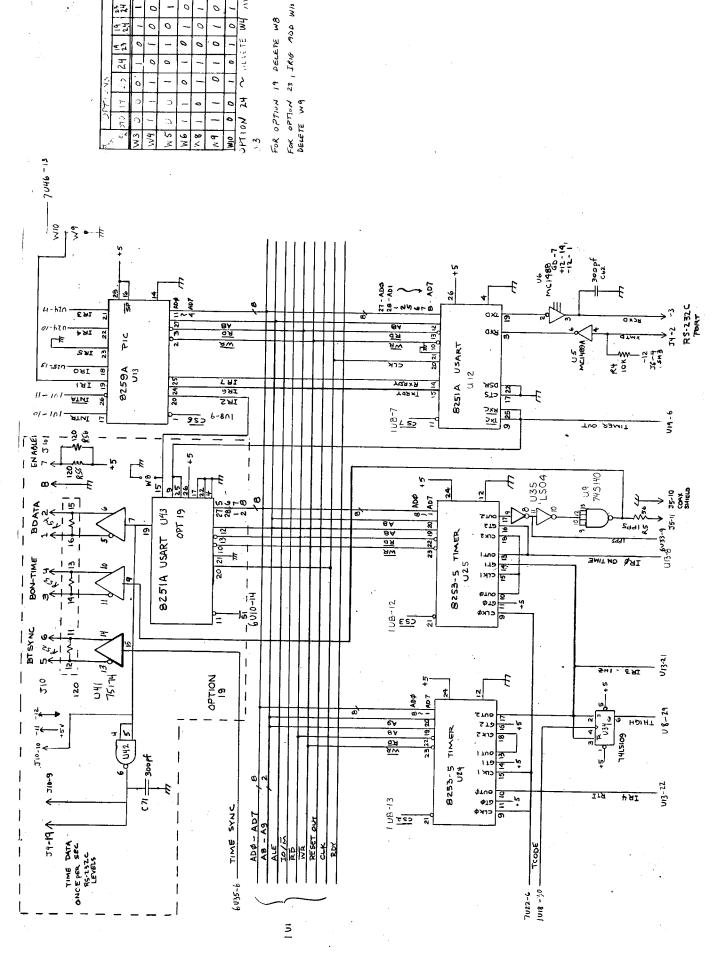

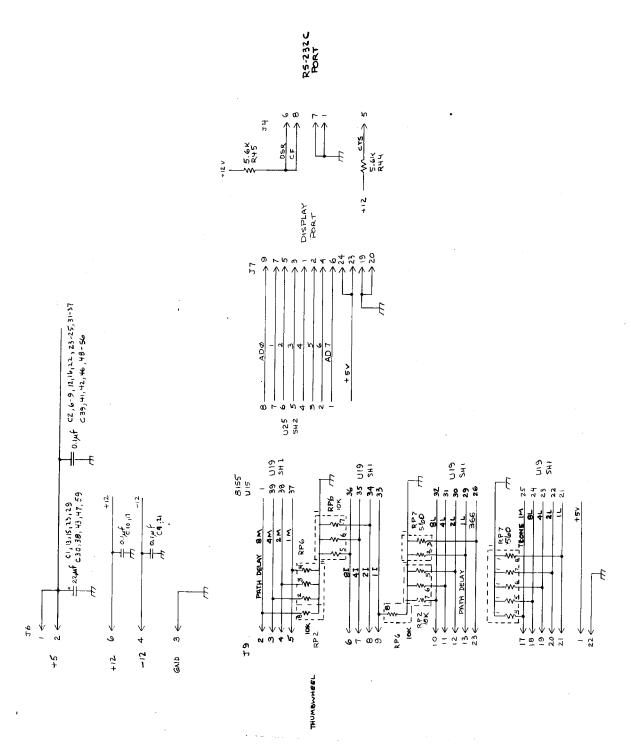

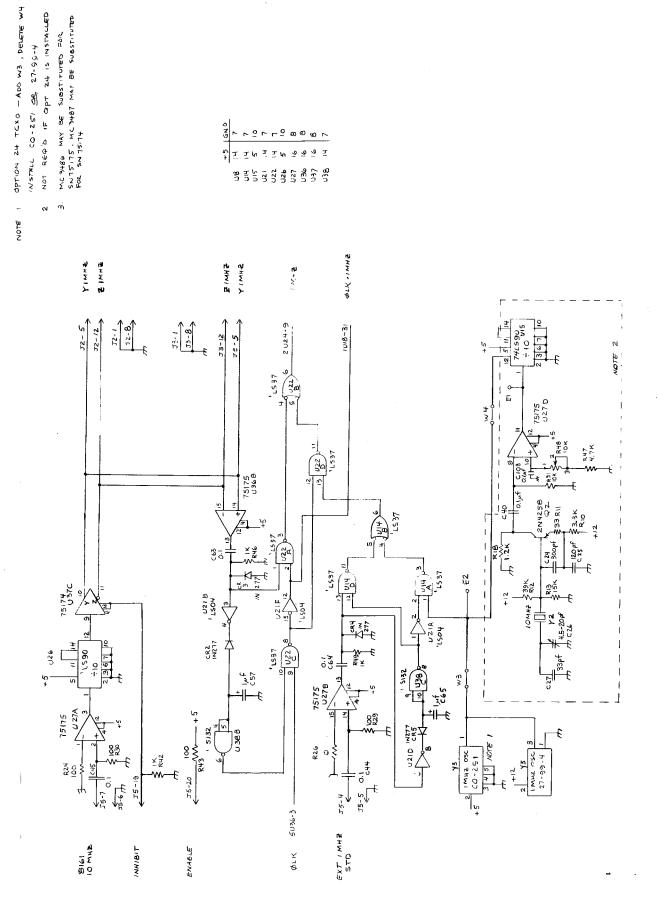

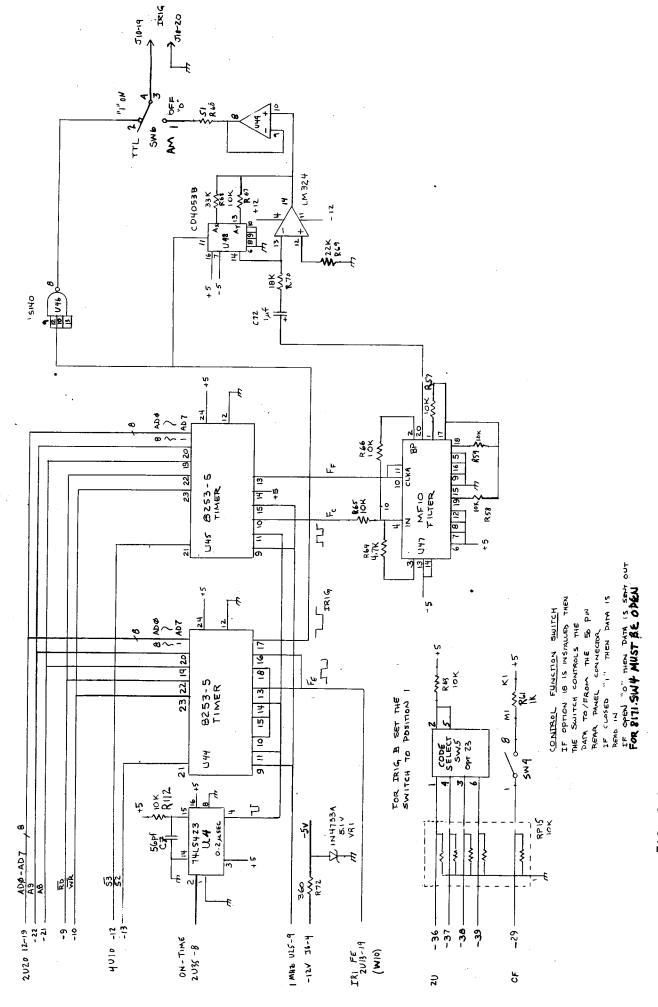

Schematics of the Microprocessor Assembly are shown in Figure 2-2, sheet 1 through 8. The Layout is shown in Figure 2-3.

References to integrated circuits identify the sheet the circuit appears on, the physical location on the board and the pin number if one is referenced. For example, 4U14B-6 refers to an IC on sheet 4, physical location U14 on the board and pin 6.

The 10-MHz output of the Model 8160A/8161/8164 Receiver is fed to the input of the first Synchronized Clock in the chain to Line Receiver 4U27A, and then is divided by 10, in Divider 4U26, to provide 1 MHz to Line Transmitter 4U37. The output of 4U37 goes to J3 for connection to the input of the next Synchronized Clock in the chain, and also to Line Receiver 4U36. Synchronized Clocks other than the first one in the chain obtain the 1 MHz signal from the previous unit through J2 to the above Line Receiver input.

FIG. 2-1 MICROPROCESSOR BLOCK DIAGRAM

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 1

2-4

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 3

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 5

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 6

SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 7 F1G. 2-2

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 8

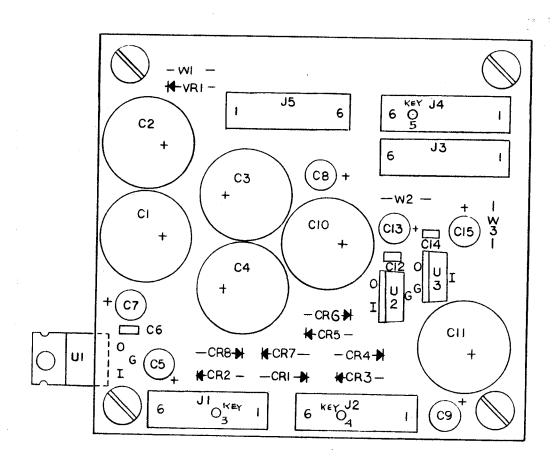

FIGURE 2-3

The 1-MHz output of 4U36 is applied to a DC restorer consisting of C63, R46, and CR3. A level detector consisting of 4U21, CR2, and C57 at the output of the DC restorer provides a positive level at the output of 4U38B in the presence of the phase locked 1-MHz signal. This signal is gated with the phase lock status signal output of the Receiver at 4U22C. If both signals are present, a ground level appears at the output of 4U22C which is inverted through 4U21F to provide the (ØLK) (1-MHz) signal to EPROM 1U18.

The 4U21F output also enables the phase locked 1-MHz signal through 4U22A.

If either the phase locked 1-MHz signal or the phase lock status signal are not present, the output of 4U22C is positive, inhibiting any signal through 4U22A and enabling 4U22D. The other input of 4U22D will be the output of one of three backup oscillators.

The three backup oscillators are an external 1-MHz standard, a temperature-compensated crystal oscillator, TCXO, (Option 24) or an uncompensated crystal oscillator.

If a 1-MHz external oscillator is used, its output will be connected through Line Receiver 4U27B. A DC restorer consisting of C64, R49, and CR4 and a level detector consisting of 4U21, CR5, and C65 operate in the same manner as the circuits described above to enable gate 4U14D and to disable gate 4U14A.

When the external signal is not present, the DC restorer and level detector inhibit gate 4U14D and enable 4U14A allowing the internal oscillator or output to be applied to OR Gate 4U14B. The output of 4U14B is gated through 4U22D. OR Gate 4U22B allows the proper 1-MHz signal to be applied to Timer 2U24. Selection of the internal oscillator or the TCXO option is performed by internal jumpers W3 and W4.

The Phase Lock Status and Time Code signals from the Receiver are each brought in to the first Synchronized Clock in the chain on connector J5 to Schmitt trigger 5U38 and then to Line Transmitter 5U37, for connection through J3 to the next unit in the chain, and also through Line Receiver 5U36 to Gate 4U22C for the Phase Lock Status signal and to EPROM 1U18 for the Time Code signal. The inputs to Synchronized Clocks other than the first in the chain are derived from the previous Synchronized Clock through connector J2 to the input of 5U36.

The 10-MHz NBS phase locked signal is fed into Line Receiver 4U27 and then to 4U26 where it is divided by 10 to 1 MHz. This signal is divided by 5000 by 2U24A to provide a 200-Hz real-time interrupt, and it is divided by 1,000,000 by 2U24B and 2U24C to provide the 1-Hz ontime reference. It is divided by 100 by 2U25A to provide a 10-KHz signal which is fed as a clock input to path delay timer 2U25B. The path delay timer is gated on by the 1-Hz reference. An output pulse

will occur after a delay proportional to the setting of the path delay thumbwheel switch on the rear panel. The signal is fed into 2025C, which is a programmable one-shot. The output is a 100-millisecond pulse whose leading edge is "on-time".

The time code, TCODE, signal is fed to Line Receiver 5036 to input pin 30 on the 8755A EPROM 1018 and to the clock input of a 74LS109 J-K flip-flop. The TCODE is sampled at a 5-millisecond rate by the microprocessor. Pulse widths are measured and decoded and the 1-Hz reference signal is phase locked to the leading edge of the time code.

The phase lock algorithm has two modes, fast sync and fine sync. In the fast sync mode, the 1-Hz reference is adjusted in 0.1-second steps until phase lock is achieved. The adjustment steps are progressively reduced to 1 millisecond. After the clock is set the steps are reduced to 0.1 millisecond. The time between adjustments is made progressively longer and will extend beyond 24 hours. Each time an adjustment is made the time and direction of the adjustment is logged in the Phase Adjust Table (See Section 1.3.5).

A serial RS-232 interface is provided by 8251A USART, 2U12. The XMTD input is received through Level Converter 2U5 and the RCXD output is sent through Level Converter 2U6. The DSR, CR, and CTS signals are connected through 5.6K ohms to +12 volts.

The processor runs under interrupt, with priorities controlled by the 8259A Programmable Interrupt Controller, PIC, 2013.

The interrupt levels are:

IRO - On-time pulse

IR1 - IRIG Frame Element (Option 23)

IR2 - Remote Output USART Xmit (Option 19)

IR3 - 1 Hz reference

IR4 - 200 Hz RTI

IR5 - On-time pulse

IR6 - USART Xmit

IR7 - USART Rcv

Chip selection is made by the LS138 1-8 Decoder, 108 and 6010. The chip selects are:

| cso - | 1U18-1         | 8755A  | EPROM & I/O                       |

|-------|----------------|--------|-----------------------------------|

| CS1 - | 1U19-8         | 8155   | RAM & I/O                         |

| CS2 - | 2U24-21        | 8253-5 | TIMER                             |

| CS3 - | 2U25-21        | 8253-5 | TIMER                             |

| CS4 - | 1U20-1         | 8755A  | EPROM & I/O                       |

| CS5 - | 1 <b>u7-</b> 8 | 74LS02 | LED DISPLAY                       |

| CS6 - | 2U13-1         | 8259A  | PROGRAMMABLE INTERRUPT CONTROLLER |

| CS7 - | 2U12-11        | 8251A  | USART                             |

| S0         | - 6U17-6                  | 8255A-5 | PROGRAMMABLE PERIPHERAL INTERFACE |

|------------|---------------------------|---------|-----------------------------------|

|            |                           |         | (PPI) (Option 18)                 |

| S1         | <ul><li>2U43-11</li></ul> | 8251A   | USART (Option 19)                 |

| S 2        | <b>-</b> 7U44-21          | 8253-5  | TIMER (Option 23)                 |

| S3         | - 7U45-21                 | 8253-5  | TIMER (Optio 23)                  |

| <b>S4</b>  | - 1U440-8                 | 8155    | RAM & I/O                         |

| <b>S</b> 5 | - 1U39-1                  | 8755A   | EPROM & I/O (Option 23)           |

The Central Processing Unit (CPU) 1U1 is an 8085A with a 6.14-MHz crystal. Power-on reset is provided on pin 36 from the brown-out reset circuitry on sheet 8. Signals RD, WR and RDY are tied to +5 volts through Resistors R1, R22 and R23.

The On-time 1 PPS output is derived from the Timer, 2U25 via Driver 2U9. Data from EPROM 1U18 is decoded and latched in PPI 6U17 to provide the parallel BCD output (Option 18) through output drivers 6U16, 6U23, and 6U28 through 6U33.

A BCD switch, 5Ull, is the data input for implementation of Selectable Bit Rate.

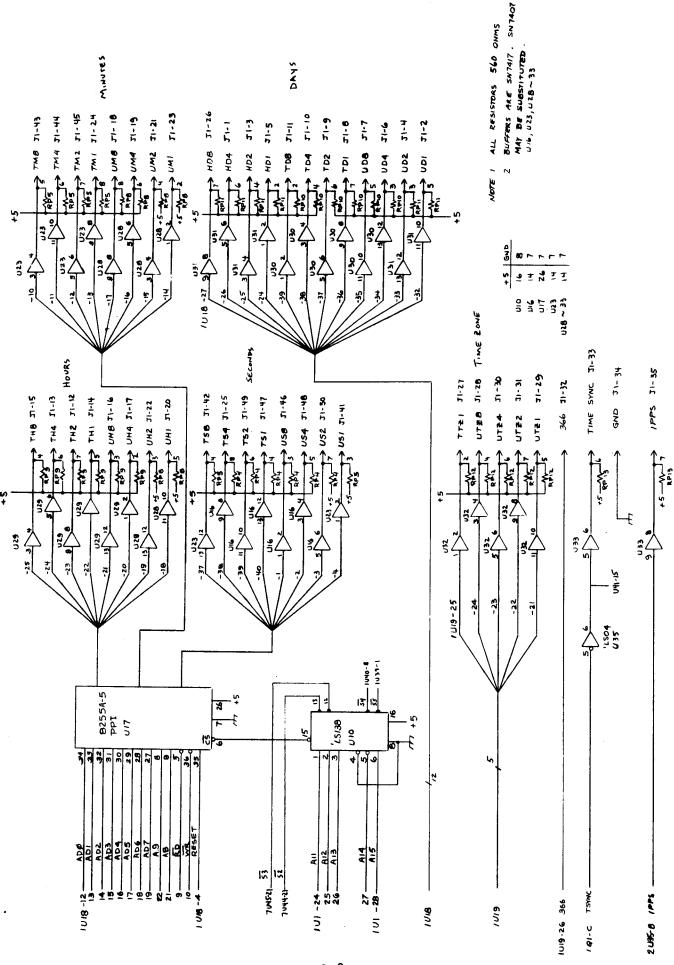

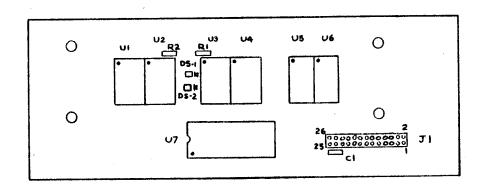

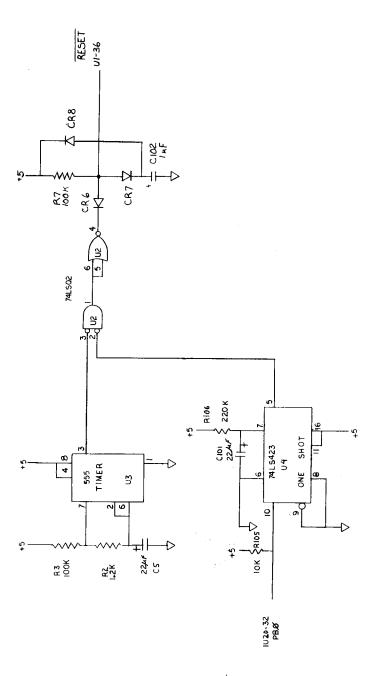

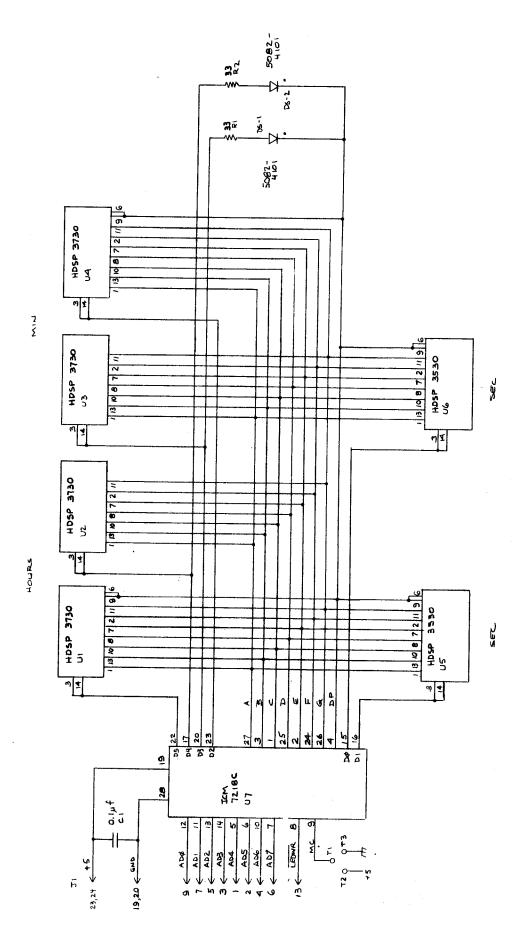

#### 2.3 DISPLAY ASSEMBLY, A2A1, P/N 014100

The Display Assembly provides digital panel readout of time of day. Prior to receiving the phase lock signal from the Receiver, time since turn-on is displayed.

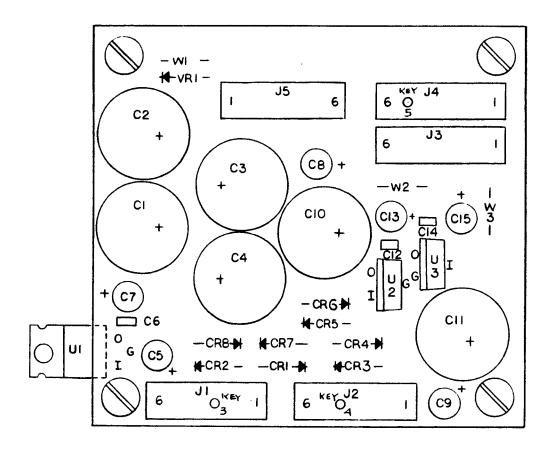

The layout of the Display Assembly is shown in Figure 2-4. The schematic is shown in Figure 2-5.

The display assembly is mounted on the rear of the front panel. It consists of ICM7218C LED Driver and six seven-segment LED digits that provide a 24-hour clock display.

FIG. 2-4 ASSEMBLY DRAWING - DISPLAY ASSEMBLY

FIG. 2-5 SCHEMATIC, DISPLAY ASSEMBLY

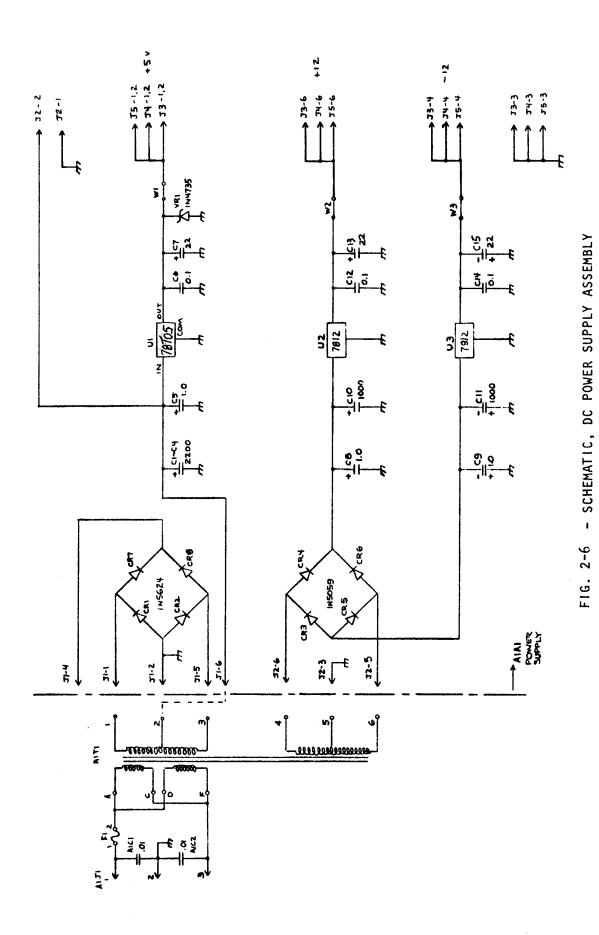

#### 2.4 DC POWER SUPPLY ASSEMBLY, A1A1, P/N 015300

The DC Power Supply Assembly provides +5 VDC, and ±12 volts DC for operation of the Microprocessor and Display Assemblies.

The layout of the DC Power Supply Assembly is shown in Figure 2-6. The schematic is shown is Figure 2-7.

The AC input for the DC power supplies is filtered by capacitors AlCl and AlC2, then fed through Fuse Fl to transformer AlT1.

The +5 volt DC supply consists of full wave rectifiers, diodes CR1 and CR2, filter capacitors C1 through C7, regulator U1 and Zener diode VR1.

The +12 volt DC supply consists of a bridge rectifier, diodes CR3 through CR6, +12 volt regulator U2, -12 volt regulator U3, and filter capacitors C8 through Cl5.

FIG. 2-6 ASSEMBLY DRAWING - DC POWER SUPPLY

2-17

FIG. 2-1 MICROPROCESSOR BLOCK DIAGRAM

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 1

7

SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET

FIGURE 2-2

2-4

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 3

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 5

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 6

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 7

FIG. 2-2 SCHEMATIC - MICROPROCESSOR ASSEMBLY - SHEET 8

FIGURE 2-3

FIG. 2-5 SCHEMATIC, DISPLAY ASSEMBLY

# 2.4 DC POWER SUPPLY ASSEMBLY, A1A1, P/N 015300

The DC Power Supply Assembly provides +5 VDC, and  $\pm 12$  volts DC for operation of the Microprocessor and Display Assemblies.

The layout of the DC Power Supply Assembly is shown in Figure 2-6. The schematic is shown is Figure 2-7.

The AC input for the DC power supplies is filtered by capacitors AlCl and AlC2, then fed through Fuse Fl to transformer AlTl.

The +5 volt DC supply consists of full wave rectifiers, diodes CR1 and CR2, filter capacitors C1 through C7, regulator U1 and Zener diode VR1.

The +12 volt DC supply consists of a bridge rectifier, diodes CR3 through CR6, +12 volt regulator U2, -12 volt regulator U3, and filter capacitors C8 through C15.

FIG. 2-6 ASSEMBLY DRAWING - DC POWER SUPPLY

# SECTION 3

## 8171A

# SERVICE INFORMATION

- 3.1 Introduction

- 3.2 Calibration

- 3.3 Test Equipment

- 3.4 Test Set-Up

- 3.5 Test Procedure

- 3.6 Trouble-shooting

#### 3.1 INTRODUCTION

This section describes how to calibrate, test, and trouble-shoot the Model 8171A. It contains the CALIBRATION procedures, a list of recommended TEST EQUIPMENT, the TEST SET-UP, TEST PROCEDURES, and a TROUBLE-SHOOTING guide.

#### 3.2 CALIBRATION

## 3.2.1 PATH DELAY AND RECEIVER DELAY CALIBRATION

There are three methods of calibration.

First Method: Provides an <u>absolute</u> accuracy of 5 to 10 milliseconds and does not require a portable clock.

Second Method: Provides a <u>relative</u> accuracy of <u>the millisecond</u> and does not require a portable clock.

Third Method: Provides 1 millisecond absolute accuracy and requires a portable clock.

First Method: Determine the path delay from Ft. Collins, Colorado, to the receiver location. See the FIG. 1-6 PATH DELAY MAP or use the formula in Section 1.3.8 Propagation Path Delay. Add to this the 17.0 millisecond nominal receiver delay. Set the rear panel thumbwheel switches to the sum of both delays:

Propagation Delay + Receiver Delay = Path Delay Switch Setting

Second Method: This method is recommended for applications that require millisecond accuracy between a group of clocks. Designate one clock as the master clock and calibrate the others against the master. The procedure is:

- 1. Calibrate the clocks by the First Method.

- 2. Let them set and run for 2-3 days. The clocks should not lose phase lock during this period. Check the Phase Lock Lost Counter, PLLC, to make sure that the units have not lost phase lock. (See Section 1, Figure 1-4 SAMPLE MEMORY DUMP, for location of PLLC). If phase lock was lost, test should be repeated.

- 3. Using an oscilloscope or time interval counter, compare the on-time pulse of the unit under test, UUT, against the master clock.

- 4. Adjust the PATH DELAY thumbwheel switch on the UUT so the time interval between the on-time pulse of the UUT and the master clock is less than 0.1 millisecond.

- 5. Repeat steps 3 and 4 for each UUT.

6. Wait 24 hours and verify that the on-time pulses are within 1 millisecond.

Third Method: This method requires a portable clock that has been calibrated. The procedure is the same as the Second Method, except the portable clock is used in place of the unit designated as the master clock.

Verification that the clock is on time to the correct second can be made by calling 303-499-7111. The audio portion of WWV signal will be heard. Verify that the clock is set correctly by observing the front panel display.

## 3.2.2 TIME BASE CALIBRATION

Calibration of the standby 10-MHz crystal oscillator is described in TEST 6. If Option 24 is present, see TEST 10 for calibration of the TCXO. The recommended calibration interval is six months.

#### 3.3 TEST EQUIPMENT

Table 3-1 lists the recommended test equipment for checking the performance of the Model 8171A.

| INSTRUMENT    | REQUIRED<br>CHARACTERISTICS                                                                | RECOMMENDED                                                        |

|---------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| WWVB Antenna  | 60 KHz Active Antenna                                                                      | Spectracom Model 8206                                              |

| WWVB Receiver | Same as Model 8161<br>with Time Code Output                                                | Spectracom Model 8160A,<br>8161, or 8164 with time<br>code output. |

| WWVB Clock    | Same as Model 8171A                                                                        | Spectracom Model 8171A                                             |

| Oscilloscope  | 2-channel                                                                                  | Tektronix Model 455                                                |

| Attenuator    | 50-ohm                                                                                     |                                                                    |

| Voltmeter     | 4-1/2-Digit Multimeter                                                                     | Data Precision Model 255                                           |

| Counter       | Accuracy 1 x 10 <sup>-7</sup>                                                              | H-P 5315B Universal<br>Counter                                     |

| TTY           | RS-232-C Teletype-<br>writer, buffered. TTY<br>must have a selectable<br>bit rate control. | Teletype KSR43                                                     |

TABLE 3-1 RECOMMENDED TEST EQUIPMENT

#### 3.4 TEST SET-UP

Install the Model 8161 WWVB Receiver/Oscillator and connect the unit to the Model 8171A with Cable A. The cable plugs into the AUX IN/OUT connector on the rear of the units.

Connect the Standard signal from the front panel of the 8161 through a 50-ohm attenuator to the EXT 1-MHZ INPUT connector on the rear panel of the 8171A. Using a BNC-T connector, connect this signal to Channel B of the oscilloscope.

Connect a buffered RS-232-C teletypewriter to the Serial ASCII port on the rear of the 8171A.

Connect a Bus Terminator (P/N 015500-2) to BUS B connector on the rear of the 8171A.

The connection of the counter, digital multimeter and oscilloscope is specified by the various tests.

FIGURE 3-1 TEST SET-UP BLOCK DIAGRAM

## 3.5 TEST PROCEDURE

Reference designations in this section refer to the sheet of the schematic and to component and pin numbers. For example, 1018-30 refers to pin 30 of integrated circuit 018 found on sheet 1 of the schematic.

# TEST 1 - VOLTAGE & FREQUENCY

The purpose of this test is to check the voltages and CPU clock frequency for their correct values.

| 1U1-40 | (+5 ±.25V)                    | V   |

|--------|-------------------------------|-----|

| 2U6-14 | (+12 ±1.2V)                   | ν   |

| 2U6-1  | $(-12 \pm 1.2 \text{V})$      | v   |

| 1U1-37 | $(3.072 \pm .03 \text{ MHz})$ | MHz |

# TEST 2 - 8161 INPUT SIGNALS

This test verifies that the signals from the 8161 are received correctly by the 8171A under test. Record the results.

Check that a 1-MHz TTL signal is present at 4U36-13.

Check that the ØLOCK signal at 5U36-3 is HIGH if the 8161 is phase locked and LOW when the 8161 is not phase locked.

Check that the TCODE signal at 5U36-5 goes high and low when the 8161 is phase locked to WWVB

# TEST 3 - THUMBWHEEL AND 366/365 SWITCH INPUTS

This test checks the proper operation of the input switches on the rear panel of the 8171A.

Set the clock manually via the TTY or automatically with WWVB.

Advance the TENS and UNITS switches on the  $\underline{\text{TZONE}}$  switch and view the front panel display for corresponding changes in the HOUR position of the display.

To check the <u>PATH DELAY</u> switches, synchronize the scope to the positive edge of the 1-Hz reference (2U34-2). Adjust the sweep to 0.1 SEC/CM. Note that the falling edge occurs at the center of the sweep.

Connect a coaxial cable to the 1 PPS ON-TIME connector on the rear panel and observe this signal on the scope. It is a positive-going 100-millisecond pulse that goes high at the center of the sweep (i.e. at the falling edge of the 1-Hz reference.)

Adjusting the <u>PATH DELAY</u> TENS, UNITS and TENTHS switches will move the 1 PPS ON-TIME pulse relative to the 1-Hz reference (2U34-2). The TENS switch will move it 10 milliseconds per digit, the UNITS, 1 millisecond, and the TENTHS, 0.1 millisecond per digit.

Adjust each digit through its range (0-9) and observe that as the switch settings are increased, the ON-TIME pulse moves to the left relative to the 1-Hz reference.

To observe these changes, the delayed sweep capability of the scope should be used.

An alternative test approach is to use the time interval measurement capability of the  $\mbox{H-P}$  5315B counter.

Test the 366/365 switch by observing that 1U19-26 is HIGH when the switch is in the 366 position and LOW when the switch is in the 365 position.

Record the results:

TIME ZONE

TENS

UNITS

PATH DELAY (2U34-2 REF, VIEW 1 PPS ON-TIME)

TENS

UNITS

TENTHS

366/365 (1U19-26 HIGH/LOW)

TEST 4 - TTY COMMANDS

Connect a TTY to the Serial ASCII port and check that the unit responds properly to the T, D, S, and X commands.

Set the switches on the TTY for FULL-DUPLEX and 300 BAUD operation.

Depress "T" and observe that the TTY prints the time message:

DDD HH:MM:SS TZ=XX (without Option 30)

WWW DDMMMYY HH:MM:SS (with Option 30)

Depress "D". The contents of the memory will be printed.

Depress "S111223344". The clock will display the time entered. (Make sure that the TZONE switch is set to 00). Depress "T" and check that the time printed corresponds to the time entered.

| Depress "X" (or any other key except T, D, or S). An "*" will be printed.                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Record the results:                                                                                                                                                                             |

| T (PRINT TIME)                                                                                                                                                                                  |

| D (DUMP MEMORY)                                                                                                                                                                                 |

| S (SET TIME)                                                                                                                                                                                    |

| X (PRINT *)                                                                                                                                                                                     |

| TEST 5 - <u>OUTPUTS</u>                                                                                                                                                                         |

| Measure the parameters of the 1 PPS ON-TIME pulse on the rear panel connector.                                                                                                                  |

| Verify that the <u>TSYNC LED</u> on the front panel comes on when the clock sets itself and stays on for 10 minutes after the antenna is disconnected, provided SW4-3,4 are both set OFF ("0"). |

| Check the display to see that all digits and the colon are operating properly.                                                                                                                  |

| 1 PPS ON-TIME (Rear Panel BNC) FREQ (1 HZ) AMPLITUDE (TTL) PULSE WIDTH (0.1 SEC) TSYNC LED (ON/OFF) DISPLAY & COLON                                                                             |

| TEST 6 - 10-MHZ STANDBY OSCILLATOR                                                                                                                                                              |

| This test checks the tuning range of the 10-MHz crystal oscillator and adjusts it to within $\pm 1 \times 10^{-6}$ .                                                                            |

| Observe the 10-MHz signal at 4U27-11. Adjust potentiometer 4R48 for a square wave. Glyptol the potentiometer.                                                                                   |

| Measure the tuning range of the oscillator by adjusting 4060.                                                                                                                                   |

| Set the frequency of the oscillator to within 10.0 MHz ±5 Hz.                                                                                                                                   |

| Record the results:                                                                                                                                                                             |

| 4U27-11 (TTL 10-MHz Square Wave)       Hz         MIN FREQUENCY 9,999,700       Hz         MAX FREQUENCY 10,000,100       Hz         SET FREQUENCY 10,000,000 ±5       Hz                       |

#### TEST 7 - EXT 1-MHZ INPUT

This test checks the input sensitivity of the EXT 1-MHZ INPUT.

Connect a 50-ohm attenuator between the 1-MHz standard and the EXT 1-MHZ INPUT connector on the rear panel.

Adjust the attenuator for 1 volt peak-to-peak output (0.35V RMS).

Observe 4U27-13 for a TTL Output.

# TEST 8 - 1-MHZ TIME BASE SELECTION

The purpose of this test is to verify that the proper 1-MHz time base is selected.

| TEST | ØLOCK<br>AND 1 MHZ<br>4U22-8 | EXT 1-MHZ<br>INPUT<br>4J5-4 | 1-MHZ<br>SELECTED<br>4U22-6 | TEST<br>RESULTS                         |

|------|------------------------------|-----------------------------|-----------------------------|-----------------------------------------|

| 8A   | 1                            | 1                           | VCXO (8161)                 |                                         |

| 8B   | 1                            | 0                           | VCXO (8161)                 |                                         |

| 8C   | 0                            | 1                           | EXT 1-MHz Input             | ****                                    |

| 8D   | 0                            | 0                           | TCXO - Opt. 24              | *************************************** |

|      |                              |                             | or XTAL OSC                 |                                         |

TEST 8A. Connect the unit as shown in Figure 3-1, TEST SET-UP BLOCK DIAGRAM. Connect Channel A of the scope to 4U22-6. Obtain phase lock to WWVB. The signal at 4U22-6 is a 1-MHz signal with a 1 to 3 microsecond jitter.

The source of the signal is the VCXO in the 8161. The jitter is a function of the signal-to-noise ratio at the antenna of the receiver.

TEST 8B. Disconnect the EXT 1-MHZ INPUT signal and observe that the signal at 4U22-6 remains unchanged.

TEST 8C. Disconnect the 8206 antenna and connect the EXT 1-MHZ INPUT. Wait until the phase lock is lost (about 30 seconds). The signal at 4U22-6 will not jitter or drift. It is derived from the same signal that is on the other channel and is synchronizing the scope.